「Cisco Catalyst 9500 アーキテクチャ ホワイトペーパー」の版間の差分

| 2行目: | 2行目: | ||

エンタープライズ キャンパス ネットワークは、アクセスレイヤにおいて 802.11ax の導入と、高速に成長するパワフルなエンドポイントにより、かつてないほど大規模な帯域幅の増加要求をサポートするよう、根底からの変化を求められています。アクセスレイヤの帯域幅は、高速側の 25Gbps や 100Gbps に合わせて実際の速度が帯域幅比率を維持できるように、1Gbps から 2.5Gbps , 5Gbps に移行しています。 | エンタープライズ キャンパス ネットワークは、アクセスレイヤにおいて 802.11ax の導入と、高速に成長するパワフルなエンドポイントにより、かつてないほど大規模な帯域幅の増加要求をサポートするよう、根底からの変化を求められています。アクセスレイヤの帯域幅は、高速側の 25Gbps や 100Gbps に合わせて実際の速度が帯域幅比率を維持できるように、1Gbps から 2.5Gbps , 5Gbps に移行しています。 | ||

| − | Cisco Catalyst 9500 シリーズ スイッチは、Cisco 新世代エンタープライズ | + | Cisco Catalyst 9500 シリーズ スイッチは、Cisco 新世代エンタープライズ クラスのバックボーンソリューションの基盤です。これらのスイッチは、エンタープライズ キャンパスをターゲット・目的とした、市場で最初の 100G 固定 1RU コア・ディストリビューションレイヤスイッチです。 |

| − | これらのスイッチは、エンタープライズ | + | これらのスイッチは、エンタープライズ アプリケーションのためのバッファリング能力と、特別なテープルのスケール (MAC , ルート数 , アクセスリスト) を提供します。このプラットフォームは、6.4Tbps までのスイッチング キャパシティと、2 Bpps (20 億 pps) の転送パフォーマンスを提供します。このプラットフォームは多様なキャンパス ニーズが求める、粒度の細かいポート密度でノン-ブロッキングの 100Gbps QSFP28 と、40Gbps の QSFP+ に加え、25Gbps SFP28 と 1/10 Gbps の SFP/SFP+ スイッチを提供します。 |

このホワイトペーパーでは、システムデザイン、電源、冷却、ストレージ オプションを含む、新しい Cisco Catalyst 9500 シリーズのアーキテクチャ概要を提供します。 | このホワイトペーパーでは、システムデザイン、電源、冷却、ストレージ オプションを含む、新しい Cisco Catalyst 9500 シリーズのアーキテクチャ概要を提供します。 | ||

=== プラットフォーム概要 === | === プラットフォーム概要 === | ||

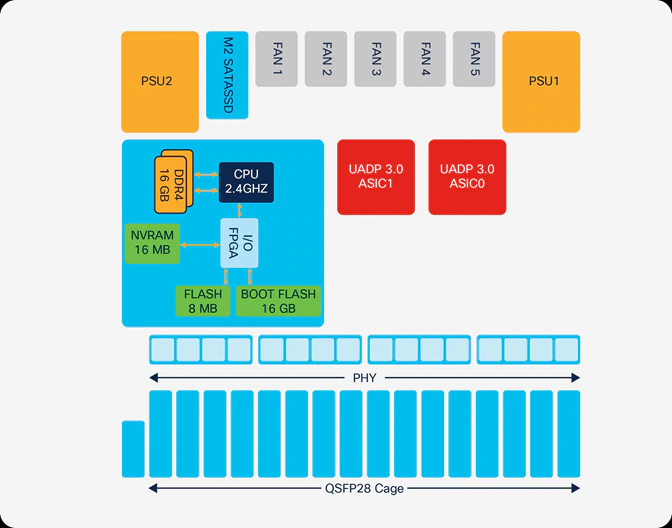

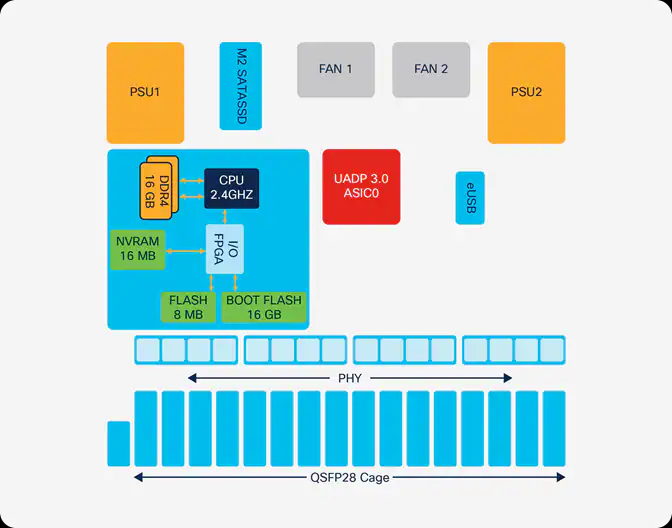

| − | Cisco Catalyst 9500 プラットフォームは固定構成から成り立ち、全面から背面のエアフローのスイッチを Cisco ユニファイドアクセス データプレーン 2.0 XL と 3. | + | Cisco Catalyst 9500 プラットフォームは固定構成から成り立ち、全面から背面のエアフローのスイッチを Cisco ユニファイドアクセス データプレーン (UADP) 2.0 XL と 3.0アーキテクチャで構成され、これは単なる投資保護だけではなく、ラージスケールと高速スループットを持たせています。このプラットフォームは、モダンなオープン Cisco IOS XE オペレーティング システムが動作し、モデル駆動プログラマビリティをサポートし、コンテナをホストするキャパシティを持ち、サードパーティ アプリをネイティブにスイッチで (x86 CPU のアーキテクチャ・ローカルストレージ・大きなメモリにしたおかげで) 動作させます。このプラットフォームはすべてのハードウェアで高可用性能力があり、プラチナ レートの冗長電源と可変速高性能ファンを持っています。Cisco Catalyst 9500 のポートフォリオ (画像 1.) は、エンタープライズ キャンパスの環境で増大するパフォーマンスへの要求に答える、多様なポートスピードとポート密度のスイッチングを提供します。 |

[[ファイル:C95 arc-01.png|なし|画像 1. Cisco Catalyst 9500 シリーズ スイッチ|代替文=|フレーム]] | [[ファイル:C95 arc-01.png|なし|画像 1. Cisco Catalyst 9500 シリーズ スイッチ|代替文=|フレーム]] | ||

| − | Catalyst 9500 | + | Catalyst 9500 ポートフォリオは、新世代ハードウェア機能とスケーラビリティによる、アーキテクチャの基礎を提供します。これらのハイ パフォーマンス スイッチは UADP 3.0 ASIC がベースとなっており、ASIC ごとに最大 3.2Tbps の転送キャパシティをサポートし、無印の C9500 が持つ UADP 2.0XL と比べて、大きなテーブルを持っています。両方の Catalyst 9500 スイッチは、類似のハードウェアアーキテクチャを持ち、実績のあるオペレーティング システム ソフトウェアによる安定性を提供します。 |

100-GE スイッチ : | 100-GE スイッチ : | ||

| 60行目: | 60行目: | ||

[[ファイル:C95 arc-04.png|なし|フレーム|画像 4. C9500-24Q/12Q ボードレイアウト]] | [[ファイル:C95 arc-04.png|なし|フレーム|画像 4. C9500-24Q/12Q ボードレイアウト]] | ||

[[ファイル:C95 arc-05.png|なし|フレーム|画像 5. C9500-40X/16X ボードレイアウト]] | [[ファイル:C95 arc-05.png|なし|フレーム|画像 5. C9500-40X/16X ボードレイアウト]] | ||

| + | |||

| 86行目: | 87行目: | ||

{| class="wikitable" | {| class="wikitable" | ||

|+ | |+ | ||

| + | テーブル 1. Cisco Catalyst 9500 AC PSU LEDs | ||

!LED | !LED | ||

!色 | !色 | ||

| 120行目: | 122行目: | ||

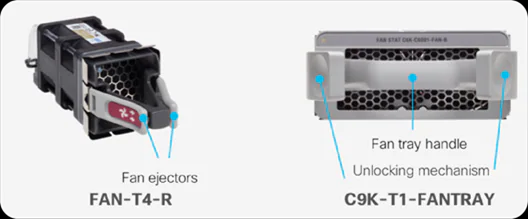

Cisco Catalyst 9500 ハイパフォーマンス SKU は、スイッチのリアに前面から背面エアフローの、ホットスワップと現地交換可能な可変速ファントレイ (ファンモジュールが 2 重になった、2 つのファントレイ) をサポートします。Cisco Catalyst 9500 UADP 2.0 XL ベースの SKU は、スイッチのリアにホットスワップと現地交換可能な可変速モジュラーファン ( 5 つの個別ファンモジュール) をサポートします。これらのファンとファントレイ ユニットは、活線挿抜と最大ファン回転数 24000rpm をサポートします。ファン ユニットは、スイッチ全体とインターフェースの冷却と、温度のしきい値を超えたときにアラームをトリガするための環境モニタに対する責任を持ちます。スイッチは複数箇所の周辺温度を監視するためのオンボード温度センサーを装備し、ファン速度を調整するための温度イベントをシステムに報告します。スイッチは 1 つの個別ファン or 1 つのファントレイのハードウェア障害まで耐えることができ、残りのファンの回転数を自動的に上げて、十分な冷却を保証します。もしスイッチが必要とする最小個数のファンを下回ったとき、スイッチはオーバーヒートからシステムを守るため、スイッチは自動的にシャットダウンされます。 | Cisco Catalyst 9500 ハイパフォーマンス SKU は、スイッチのリアに前面から背面エアフローの、ホットスワップと現地交換可能な可変速ファントレイ (ファンモジュールが 2 重になった、2 つのファントレイ) をサポートします。Cisco Catalyst 9500 UADP 2.0 XL ベースの SKU は、スイッチのリアにホットスワップと現地交換可能な可変速モジュラーファン ( 5 つの個別ファンモジュール) をサポートします。これらのファンとファントレイ ユニットは、活線挿抜と最大ファン回転数 24000rpm をサポートします。ファン ユニットは、スイッチ全体とインターフェースの冷却と、温度のしきい値を超えたときにアラームをトリガするための環境モニタに対する責任を持ちます。スイッチは複数箇所の周辺温度を監視するためのオンボード温度センサーを装備し、ファン速度を調整するための温度イベントをシステムに報告します。スイッチは 1 つの個別ファン or 1 つのファントレイのハードウェア障害まで耐えることができ、残りのファンの回転数を自動的に上げて、十分な冷却を保証します。もしスイッチが必要とする最小個数のファンを下回ったとき、スイッチはオーバーヒートからシステムを守るため、スイッチは自動的にシャットダウンされます。 | ||

[[ファイル:C95 arc-08.png|なし|フレーム|画像 8. Cisco Catalyst 9500 ファンとファントレイ]] | [[ファイル:C95 arc-08.png|なし|フレーム|画像 8. Cisco Catalyst 9500 ファンとファントレイ]] | ||

| − | |||

ファンモジュールの挿入と抜去は、ファンアセンブリのイジェクトレバーで簡単に行なえます。ファン イジェクトレバーを押し、ファンのハンドルを持ってモジュールを挿入、または抜去します。テーブル 2. にファンとファントレイの状態を示す LED を記載します。 | ファンモジュールの挿入と抜去は、ファンアセンブリのイジェクトレバーで簡単に行なえます。ファン イジェクトレバーを押し、ファンのハンドルを持ってモジュールを挿入、または抜去します。テーブル 2. にファンとファントレイの状態を示す LED を記載します。 | ||

| 126行目: | 127行目: | ||

{| class="wikitable" | {| class="wikitable" | ||

|+ | |+ | ||

| + | テーブル 2. Cisco Catalyst 9500 ファン・ファン トレイ LEDs | ||

!LED | !LED | ||

!色 | !色 | ||

| 154行目: | 156行目: | ||

Catalyst 9500 は、特定の機能をサポートを最適化し、システムリソースを設定・提供する、ラインレートのスイッチです。リソースはネットワークでスイッチの使用用途に応じて変更できます。スイッチのアーキテクチャは 4 つのメインコンポーネントから成り立っています。 | Catalyst 9500 は、特定の機能をサポートを最適化し、システムリソースを設定・提供する、ラインレートのスイッチです。リソースはネットワークでスイッチの使用用途に応じて変更できます。スイッチのアーキテクチャは 4 つのメインコンポーネントから成り立っています。 | ||

| − | UADP ASIC 複合体 | + | * UADP ASIC 複合体 |

| − | + | * X86 CPU 複合体 | |

| − | X86 CPU 複合体 | + | * ASIC 相互接続 |

| − | + | * フロントパネル インターフェース | |

| − | ASIC 相互接続 | ||

| − | |||

| − | フロントパネル インターフェース | ||

画像 10. に、スイッチ コンポーネントのハイ レベル 構成図を示します。 | 画像 10. に、スイッチ コンポーネントのハイ レベル 構成図を示します。 | ||

| 166行目: | 165行目: | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

=== UADP ASIC 複合体 === | === UADP ASIC 複合体 === | ||

Catalyst 9500 シリーズスイッチは、2 種類の UADP ASIC で構築されています : UADP 2.0 XL と UADP 3.0 です。両方ともシステム・オン・チップ (SoC) アーキテクチャがベースになっています。両方の ASIC でそのアーキテクチャは似通っていますが、そのバージョンの違いはスイッチングキャパシティ、ポート速度、バッファリング能力、そして転送のスケーラビリティです。 | Catalyst 9500 シリーズスイッチは、2 種類の UADP ASIC で構築されています : UADP 2.0 XL と UADP 3.0 です。両方ともシステム・オン・チップ (SoC) アーキテクチャがベースになっています。両方の ASIC でそのアーキテクチャは似通っていますが、そのバージョンの違いはスイッチングキャパシティ、ポート速度、バッファリング能力、そして転送のスケーラビリティです。 | ||

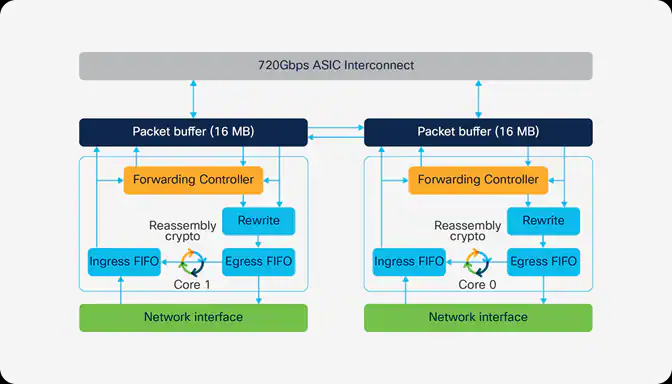

| − | UADP 2.0 XL は第 3 世代で、次世代 Catalyst の固定 or モジュラースイッチに最適化された、240G デュアルコア ASIC です。UADP 2.0 XL のアーキテクチャと機能は、全世代の UADP ASIC から大きくは変わっていません。その UADP 2.0 XL ASIC はデュアルコア アーキテクチャの 28 | + | UADP 2.0 XL は第 3 世代で、次世代 Catalyst の固定 or モジュラースイッチに最適化された、240G デュアルコア ASIC です。UADP 2.0 XL のアーキテクチャと機能は、全世代の UADP ASIC から大きくは変わっていません。その UADP 2.0 XL ASIC はデュアルコア アーキテクチャの 28 ナノメーター技術で構築されています。画像 11. に UADP XL ASIC のコンポーネントを示します。 |

[[ファイル:C95 arc-11.png|なし|フレーム|画像 11. UADP 2.0 XL ブロック ダイアグラム]] | [[ファイル:C95 arc-11.png|なし|フレーム|画像 11. UADP 2.0 XL ブロック ダイアグラム]] | ||

| − | |||

UADP 2.0 XL のキーとなる能力 : | UADP 2.0 XL のキーとなる能力 : | ||

| − | * パケット・スイッチング帯域幅 : 240G (コアあたり 120G) | + | * '''パケット・スイッチング帯域幅 :''' 240G (コアあたり 120G) |

| − | * 転送パフォーマンス : 375Mpps | + | * '''転送パフォーマンス :''' 375Mpps |

| − | * スタック帯域幅 720G (2x360G / リング) | + | * '''スタック帯域幅 :''' 720G (2x360G / リング) |

| − | * FIB テーブル : 128K/64K IPv4 / IPv6 ホストルートと、64K/32K IPv4 / IPv6 最長プレフィクス該当エントリ | + | * '''FIB テーブル :''' 128K/64K IPv4 / IPv6 ホストルートと、64K/32K IPv4 / IPv6 最長プレフィクス該当エントリ |

| − | * 共有パケットバッファ : 32MB (コアあたり 16MB) | + | * '''共有パケットバッファ :''' 32MB (コアあたり 16MB) |

| − | * 専用 NetFlow ブロック : 128K(IPv4) / 64K(IPv6) (コアあたり 64K/32K) | + | * '''専用 NetFlow ブロック :''' 128K(IPv4) / 64K(IPv6) (コアあたり 64K/32K) |

| − | * TCAM ACL : 54K 全体キャパシティ | + | * '''TCAM ACL :''' 54K 全体キャパシティ |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

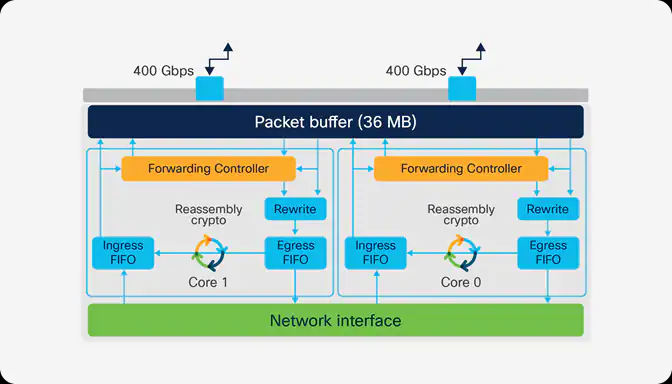

| + | UADP 3.0 ASIC は、UADP 2.0 アーキテクチャをベースにした次世代のもので、16 ナノメーター技術により、他のすべての UADP ASICs と比べて、さらに大きなテーブルと帯域幅を提供します。画像 12. に UADP 3.0 ASIC のコンポーネントを示します。[[ファイル:C95 arc-12.png|なし|フレーム|画像 12. UADP 3.0 ASIC ブロック ダイアグラム]] | ||

UADP 3.0 のキーとなる能力 : | UADP 3.0 のキーとなる能力 : | ||

| − | * パケット・スイッチング帯域幅 : 1600G (コアあたり 800G) | + | * '''パケット・スイッチング帯域幅 :''' 1600G (コアあたり 800G) |

| − | * 転送パフォーマンス : 1Bpps (コアあたり 500Mpps) | + | * '''転送パフォーマンス :''' 1Bpps (コアあたり 500Mpps) |

| − | * ASIC 相互接続 : 合計 800G 帯域幅を持つ、2 つのポイント・ツー・ポイント リンク | + | * '''ASIC 相互接続 :''' 合計 800G 帯域幅を持つ、2 つのポイント・ツー・ポイント リンク |

| − | * FIB テーブル : IPv6 の構築に最適化された、416K の 2 倍幅テーブル | + | * '''FIB テーブル :''' IPv6 の構築に最適化された、416K の 2 倍幅テーブル |

| − | * ユニファイド パケットバッファ : 両方のコアで共有の 36MB | + | * '''ユニファイド パケットバッファ :''' 両方のコアで共有の 36MB |

| − | * 専用 NetFlow ブロック : 128K(IPv4) まで、IPv6 2 倍幅共有テーブル | + | * '''専用 NetFlow ブロック :''' 128K(IPv4) まで、IPv6 2 倍幅共有テーブル |

| − | * TCAM ACL : 54K 全体キャパシティ | + | * '''TCAM ACL :''' 54K 全体キャパシティ |

| − | + | '''ノート :''' UADP 3.0 はパケット サイズ 187 バイト以上でラインレートの転送パフォーマンスを獲得しています テーブル 3. に UADP 2.0 XL と UADP 3.0 ASICs のハイレベル差分を示します | |

| − | '''ノート :''' UADP 3.0 はパケット サイズ 187 | ||

{| class="wikitable" | {| class="wikitable" | ||

| 268行目: | 253行目: | ||

=== ASIC 相互接続 === | === ASIC 相互接続 === | ||

| − | Catalyst 9500 | + | Catalyst 9500 スイッチは、スタックポートが無い、固定型のコアと集約スイッチです。スタックポートが無いことから、ASIC 相互接続リンクは ASIC 間のコミュニケーションに使用されます。コミュニケーションは ASIC のコアもしくはコア間でローカルにスイッチングされ、ASIC 内のローカルポートに向かうパケットは ASIC 相互接続リンクを使用しません。ASIC 相互接続の目的は、複数の UADP ASICs 間のデータ移動にあります。 |

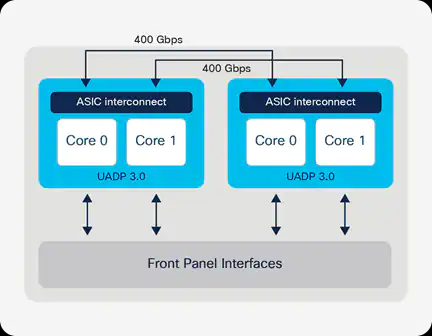

UADP 3.0 は 2 つの相互接続リンクを持ち、全体のパケット帯域幅は 800Gbps になります。 | UADP 3.0 は 2 つの相互接続リンクを持ち、全体のパケット帯域幅は 800Gbps になります。 | ||

| 292行目: | 277行目: | ||

イーサネット物理レイヤ (PHY) は、リンク層デバイス (多くの場合は MAC) を、トランシーバなどの物理媒体に接続します。PHY は Catalyst 9500 スイッチではイーサネットトランシーバに完全に統合されており、フロントパネルポートに挿入されたオプティクスで複数の速度 (10,25,40,100GE) をサポートするため、ASIC レーンのステアリングとマッピングをサポートします。 | イーサネット物理レイヤ (PHY) は、リンク層デバイス (多くの場合は MAC) を、トランシーバなどの物理媒体に接続します。PHY は Catalyst 9500 スイッチではイーサネットトランシーバに完全に統合されており、フロントパネルポートに挿入されたオプティクスで複数の速度 (10,25,40,100GE) をサポートするため、ASIC レーンのステアリングとマッピングをサポートします。 | ||

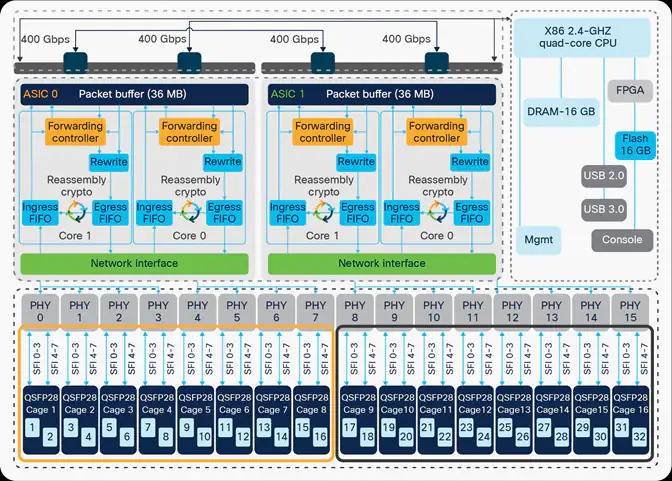

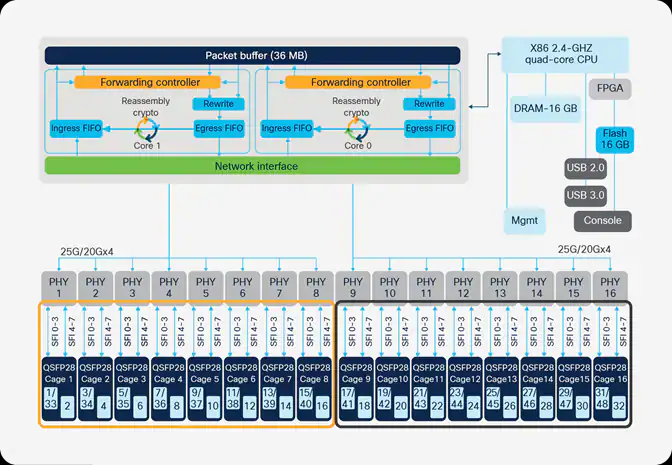

| − | [[ファイル:C95 arc-16.png|なし|フレーム|画像 16. C9500-32C ハイレベル ブロック ダイアグラム]] | + | [[ファイル:C95 arc-16.png|なし|フレーム|画像 16. C9500-32C ハイレベル ブロック ダイアグラム]] |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

==== C9500-32C スイッチのハイライトは以下の通りです : ==== | ==== C9500-32C スイッチのハイライトは以下の通りです : ==== | ||

| 322行目: | 283行目: | ||

* 2x1 コンフィギュレーションモードに 16 列の QSFP28 ケージ | * 2x1 コンフィギュレーションモードに 16 列の QSFP28 ケージ | ||

* それぞれの QSFP28 ケージは、ASIC に向かう 8 つのノースバウンド SERDES 接続を持ちます | * それぞれの QSFP28 ケージは、ASIC に向かう 8 つのノースバウンド SERDES 接続を持ちます | ||

| − | ** それぞれの SERDES は次のどちらかで動作します。40G QSFP+ オプティクスで 4x10G | + | ** それぞれの SERDES は次のどちらかで動作します。40G QSFP+ オプティクスで 4x10G スピード もしくは 100G QSFP28 オプティクスで4x25G スピード |

| − | ** インターフェーススピードは、挿入されたトランシーバ | + | ** インターフェーススピードは、挿入されたトランシーバ モジュールがベースになります |

* 32 QSFP28 イーサネットポート | * 32 QSFP28 イーサネットポート | ||

** QSFP+ / QSFP28 トランシーバモジュールによる 40G or 100G or CVR アダプタ + SFP による 10G/1G | ** QSFP+ / QSFP28 トランシーバモジュールによる 40G or 100G or CVR アダプタ + SFP による 10G/1G | ||

| 337行目: | 298行目: | ||

==== C9500-32QC スイッチのハイライトは以下の通りです : ==== | ==== C9500-32QC スイッチのハイライトは以下の通りです : ==== | ||

| − | * 2x1 コンフィギュレーションモードに 16 列の QSFP28 | + | * 2x1 コンフィギュレーションモードに 16 列の QSFP28 ケージ |

| − | * それぞれの QSFP28 ケージは、ASIC に向かう 4 つのノースバウンド SERDES | + | * それぞれの QSFP28 ケージは、ASIC に向かう 4 つのノースバウンド SERDES 接続を持ちます |

| − | ** それぞれの SERDES は次のどちらかで動作します。40G QSFP+ オプティクスで 2x20G | + | ** それぞれの SERDES は次のどちらかで動作します。40G QSFP+ オプティクスで 2x20G スピード もしくは 100G QSFP28 オプティクスで4x25G スピード |

| − | ** インターフェーススピードは、CLI | + | ** インターフェーススピードは、CLI ベース |

| − | * 32 QSFP28 | + | * 32 QSFP28 イーサネットポート |

| − | ** QSFP+ / QSFP28 トランシーバモジュールによる 40G or 100G or CVR アダプタ + SFP による 10G/1G | + | ** QSFP+ / QSFP28 トランシーバモジュールによる 40G or 100G or CVR アダプタ + SFP による 10G/1G |

* ポートマッピング | * ポートマッピング | ||

| − | ** ポート 1-16 は ASIC 0 / コア 1 , ポート 17-32 は ASIC 0 / コア 0 | + | ** ポート 1-16 は ASIC 0 / コア 1 , ポート 17-32 は ASIC 0 / コア 0 にマッピング |

| − | * オプティクスの電源はオンボードコントローラによって行われ、フロント パネル | + | * オプティクスの電源はオンボードコントローラによって行われ、フロント パネル ケージに挿入されたモジュールで使用されます |

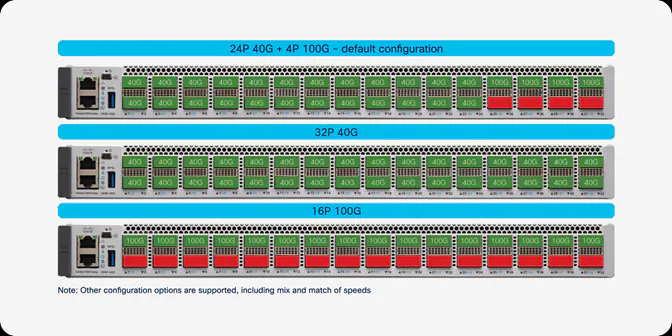

* デフォルトポート コンフィギュレーションは、 | * デフォルトポート コンフィギュレーションは、 | ||

| − | ** ポート 1-24 は 40G | + | ** ポート 1-24 は 40G インターフェースとして有効化・アクティブになります |

| − | ** ポート 25-32 は 40G | + | ** ポート 25-32 は 40G インターフェースですが、インアクティブです |

| − | ** ポート 45-48 は 100G | + | ** ポート 45-48 は 100G インターフェースとしてアクティブになります |

| − | ** 100G ポートの有効化 or 無効化は、"enable / no enable" インターフェース | + | ** 100G ポートの有効化 or 無効化は、"enable / no enable" インターフェース コマンドを使用して行います |

| − | * アドバンスド フォワーディング ASIC は、100Gbps シングル フロー トラフィック処理を 100G 設定ポートでサポートし、20G シングル フロー トラフィック処理をすべての 40G | + | * アドバンスド フォワーディング ASIC は、100Gbps シングル フロー トラフィック処理を 100G 設定ポートでサポートし、20G シングル フロー トラフィック処理をすべての 40G ポートでサポートします |

2021年3月21日 (日) 11:18時点における版

イントロダクション

エンタープライズ キャンパス ネットワークは、アクセスレイヤにおいて 802.11ax の導入と、高速に成長するパワフルなエンドポイントにより、かつてないほど大規模な帯域幅の増加要求をサポートするよう、根底からの変化を求められています。アクセスレイヤの帯域幅は、高速側の 25Gbps や 100Gbps に合わせて実際の速度が帯域幅比率を維持できるように、1Gbps から 2.5Gbps , 5Gbps に移行しています。

Cisco Catalyst 9500 シリーズ スイッチは、Cisco 新世代エンタープライズ クラスのバックボーンソリューションの基盤です。これらのスイッチは、エンタープライズ キャンパスをターゲット・目的とした、市場で最初の 100G 固定 1RU コア・ディストリビューションレイヤスイッチです。

これらのスイッチは、エンタープライズ アプリケーションのためのバッファリング能力と、特別なテープルのスケール (MAC , ルート数 , アクセスリスト) を提供します。このプラットフォームは、6.4Tbps までのスイッチング キャパシティと、2 Bpps (20 億 pps) の転送パフォーマンスを提供します。このプラットフォームは多様なキャンパス ニーズが求める、粒度の細かいポート密度でノン-ブロッキングの 100Gbps QSFP28 と、40Gbps の QSFP+ に加え、25Gbps SFP28 と 1/10 Gbps の SFP/SFP+ スイッチを提供します。

このホワイトペーパーでは、システムデザイン、電源、冷却、ストレージ オプションを含む、新しい Cisco Catalyst 9500 シリーズのアーキテクチャ概要を提供します。

プラットフォーム概要

Cisco Catalyst 9500 プラットフォームは固定構成から成り立ち、全面から背面のエアフローのスイッチを Cisco ユニファイドアクセス データプレーン (UADP) 2.0 XL と 3.0アーキテクチャで構成され、これは単なる投資保護だけではなく、ラージスケールと高速スループットを持たせています。このプラットフォームは、モダンなオープン Cisco IOS XE オペレーティング システムが動作し、モデル駆動プログラマビリティをサポートし、コンテナをホストするキャパシティを持ち、サードパーティ アプリをネイティブにスイッチで (x86 CPU のアーキテクチャ・ローカルストレージ・大きなメモリにしたおかげで) 動作させます。このプラットフォームはすべてのハードウェアで高可用性能力があり、プラチナ レートの冗長電源と可変速高性能ファンを持っています。Cisco Catalyst 9500 のポートフォリオ (画像 1.) は、エンタープライズ キャンパスの環境で増大するパフォーマンスへの要求に答える、多様なポートスピードとポート密度のスイッチングを提供します。

Catalyst 9500 ポートフォリオは、新世代ハードウェア機能とスケーラビリティによる、アーキテクチャの基礎を提供します。これらのハイ パフォーマンス スイッチは UADP 3.0 ASIC がベースとなっており、ASIC ごとに最大 3.2Tbps の転送キャパシティをサポートし、無印の C9500 が持つ UADP 2.0XL と比べて、大きなテーブルを持っています。両方の Catalyst 9500 スイッチは、類似のハードウェアアーキテクチャを持ち、実績のあるオペレーティング システム ソフトウェアによる安定性を提供します。

100-GE スイッチ :

- C9500-32C - Cisco Catalyst 9500 ハイパフォーマンス シリーズ 2xUADP 3.0 ASIC と 32x 100GE QSFP28 ポート

- C9500-32QC - Cisco Catalyst 9500 ハイパフォーマンス シリーズ UADP 3.0 ASIC と 32x 40GE or 16x 100GE QSFP28 ポート

40GE スイッチ :

- C9500-24Q - Cisco Catalyst 9500 シリーズ 4xUADP 2.0 XL ASIC と 24x 40GE QSFP+ ポート

- C9500-12Q - Cisco Catalyst 9500 シリーズ 2xUADP 2.0 XL ASIC と 12x 40GE QSFP+ ポート

25GE スイッチ :

- C9500-48Y4C - Cisco Catalyst 9500 ハイパフォーマンス シリーズ UADP 3.0 ASIC と 48x 25GE SFP28 と 4x100/40GE QSFP28 ポート

- C9500-24Y4C - Cisco Catalyst 9500 ハイパフォーマンス シリーズ UADP 3.0 ASIC と 24x 25GE SFP28 と 4x100/40GE QSFP28 ポート

10GE スイッチ:

- C9500-40X - Cisco Catalyst 9500 シリーズ 2xUADP 2.0 XL ASIC と 40x10GE SFP+ + 2x40/8x10GE ポート

- C9500-16X - Cisco Catalyst 9500 シリーズ UADP 2.0 XL ASIC と16x10GE SFP+ + 2x40/8x10GE ポート

ノート : Cisco Catalyst 9500 シリーズの型式ネーミング ルールは、サポートするポートのスピードを含んでいます

C9500 - Catalyst スイッチ ファミリーであることを示す

- X: Native 10-GE フロントパネル ポート

- Y: Native 25-GE フロントパネル ポート

- Q: Native 40-GE フロントパネル ポート

- C: Native 100-GE フロントパネル ポート

スイッチの概要

このセクションでは、Catalyst 9500 シリーズスイッチの高レベルな見どころを説明します。Catalyst 9500 スイッチは、以下をサポートします:

- 8 個の SKU オプション : システムに最適なポートスピード・ポート密度・ネットワーク スケールを選択してください。

- 2 個までのプラチナ レート PSU : 1.6KW AC/DC か 950W/930W AC/DC 電源は、1:1 の電源冗長

- 新世代高効率可変速ファン : N+1 か 1+1 ファン/ファントレイ 冗長と、最大 24000 RPM のファンスピード

- マルチレート オプティクス : すべての QSFP28 ポートが異なるスピードの 100/40/25/10/1G をサポートし、すべての QSFP+ ポートが異なるスピードの 4010/1G をサポート

- 120G USB3.0 か、960G M2 SATA 外部 SSD ストレージ : 主にサードパーティ アプリケーションのホスティング用

スイッチデザイン

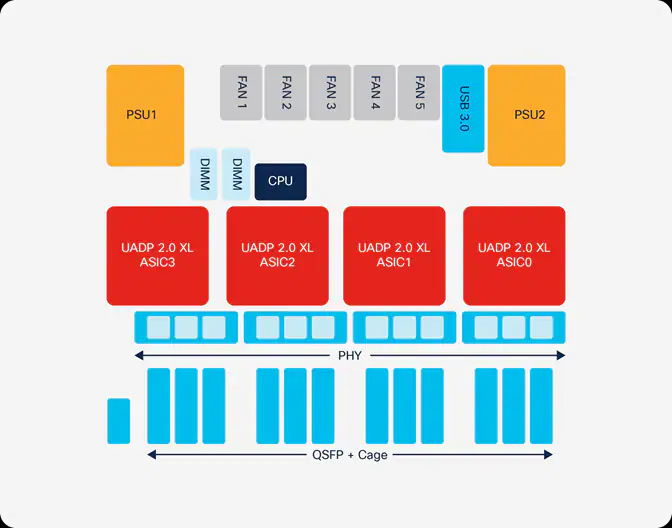

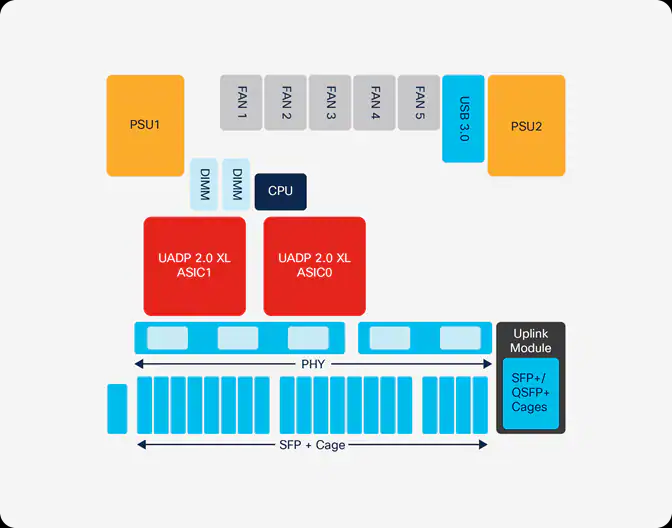

エンタープライズ ネットワークでは 25G と 100Gbps のように高速を目指して移行していますが、レポートによると固定スイッチが密度・コスト・電力に大きなメリットをもたらすため、モジュラー スイッチの出荷は減少しています。このセクションでは、新 Cisoc Catalyst 9500 シリーズ スイッチのハイレベル システム デザインを簡潔にカバーします。画像 2,3,4,5 は異なるボードのレイアウトを表示しています。

Catalyst 9500 スイッチは、フロントパネル ポートに RJ45 コンソールポート、USB ミニ タイプ B コンソールポート、RJ45 管理ポート、フラッシュドライブ用の USB タイプ A 2.0/3.0 ホストポートを持っています。すべてのスイッチは、インベントリ管理用にパッシブな組み込み RFID があり、スイッチの識別用にブルービーコン LED とシステムステータス表示用に 3 色 LED を持っています。

Catalyst 9500 のリアパネルには、現地交換が可能なパワー・サプライ・ユニット (PSU) スロットと、現地交換が可能な冗長可変速ファン、もしくは 2 のファントレイ ユニット、そして M2 SATA ドライブかストレージ用の USB 3.0 ドライブがあります。

スイッチ電源

Cisco Catalyst 9500 ハイパフォーマンススイッチは、1.6KW か 650W の全体システム キャパシティのために、2 つの 1.6KW/650W AC か、1.6KW/930W DC の小型フォームファクターのパワー・サプライ・ユニット (PSUs) を持ちます (画像 6.) 。Catalyst 9500 UADP 2.0 XL を持つ型式の機種では、950W の全体システム キャパシティのために、2 つの 950W AC/DC PSUs を持ちます。それぞれの PSU は 100% の負荷で 90% を超える変換効率を持つ、プラチナ レートの電源です。システムは非冗長モードの 1 PSU があり、それは最大構成でスイッチを駆動するのに十分でです。もしくは冗長負荷分散モードの 2 PSU があり、それぞれの PSU から 50% の電力を減少させます。電源は AC と DC の療法をサポートし、AC と DC の組み合わせと、活線挿抜 (OIR) 機能をサポートします。

電源

Catalyst 9500 スイッチの電源ごとの最大出力電流は :

- 1.6KW AC PSU で 220V 入力のとき 1.6KW と 110V 入力のとき 1000W

- 950W AC PSU で 110-220V 入力のとき 950W

- 930W AC PSU で 110-220V 入力のとき 930W

それぞれの PSU は、100% 負荷で約 20 ミリ秒の瞬断でも電力を維持する能力を持っています。それぞれの PSU は、前面から背面方向の可変速冷却ファンが付属しており、シンプルでセキュアな OIR のために、プッシュ リリースロックを持っています。画像 7. にスイッチの PSU 機能を示します。

それぞれの PSU は電源の状態を確認するために、2 色 (緑・橙) の LED をサポートします。点灯パターンをテーブル 1. に示します。

| LED | 色 | 状態 | 備考 |

|---|---|---|---|

| 緑 | off | 電源入力なし | |

| 緑 | 点滅 | 12V メインがオフ、12V スタンバイ電源がオン | |

| 緑 | 点灯 | 12V メインがオン | |

| 橙 | 点滅 | 12V メインで警告が検出 | |

| 橙 | 点灯 | クリティカル エラーが検出 |

スイッチの冷却

Cisco Catalyst 9500 ハイパフォーマンス SKU は、スイッチのリアに前面から背面エアフローの、ホットスワップと現地交換可能な可変速ファントレイ (ファンモジュールが 2 重になった、2 つのファントレイ) をサポートします。Cisco Catalyst 9500 UADP 2.0 XL ベースの SKU は、スイッチのリアにホットスワップと現地交換可能な可変速モジュラーファン ( 5 つの個別ファンモジュール) をサポートします。これらのファンとファントレイ ユニットは、活線挿抜と最大ファン回転数 24000rpm をサポートします。ファン ユニットは、スイッチ全体とインターフェースの冷却と、温度のしきい値を超えたときにアラームをトリガするための環境モニタに対する責任を持ちます。スイッチは複数箇所の周辺温度を監視するためのオンボード温度センサーを装備し、ファン速度を調整するための温度イベントをシステムに報告します。スイッチは 1 つの個別ファン or 1 つのファントレイのハードウェア障害まで耐えることができ、残りのファンの回転数を自動的に上げて、十分な冷却を保証します。もしスイッチが必要とする最小個数のファンを下回ったとき、スイッチはオーバーヒートからシステムを守るため、スイッチは自動的にシャットダウンされます。

ファンモジュールの挿入と抜去は、ファンアセンブリのイジェクトレバーで簡単に行なえます。ファン イジェクトレバーを押し、ファンのハンドルを持ってモジュールを挿入、または抜去します。テーブル 2. にファンとファントレイの状態を示す LED を記載します。

| LED | 色 | 状態 | 備考 |

|---|---|---|---|

| ファン | オフ | 電源入力なし | |

| ファン | 点滅 | 12V メインがオフ、12V スタンバイ電源がオン | |

| ファン | 点灯 | クリティカル エラーが検出 |

スイッチのエアフロー

Cisco Catalyst 9500 ファンとファントレイは、前面から背面のエアフローをサポートします。エアフローの排出を画像 9. に示します。

9500 スイッチは、すべての C9500 SKU でポート面の吸気をサポートし、前面 (コールドアイル) のポート面から冷やす空気を取り入れ、背面 (ホットアイル) のファンと電源モジュールから暖かくなった空気を排気します。QSFP/SFP のケージは、ケージを通る中央部のエアフローで熱的に強化されています。

ベースボード コンポーネント

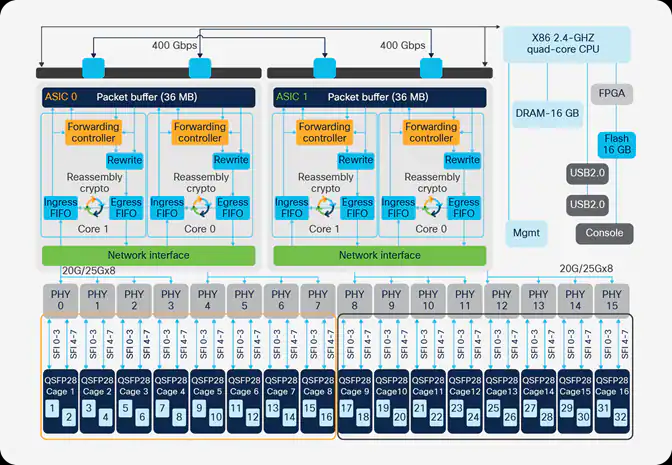

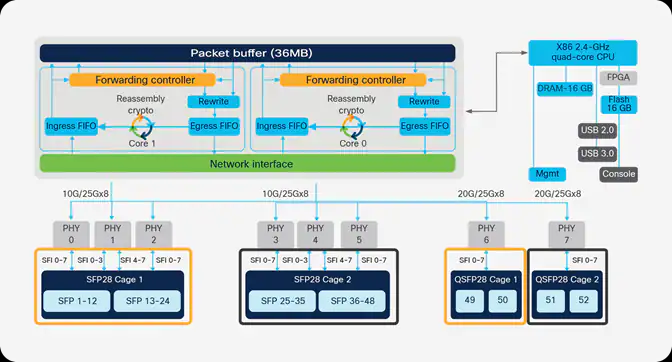

Catalyst 9500 は、特定の機能をサポートを最適化し、システムリソースを設定・提供する、ラインレートのスイッチです。リソースはネットワークでスイッチの使用用途に応じて変更できます。スイッチのアーキテクチャは 4 つのメインコンポーネントから成り立っています。

- UADP ASIC 複合体

- X86 CPU 複合体

- ASIC 相互接続

- フロントパネル インターフェース

画像 10. に、スイッチ コンポーネントのハイ レベル 構成図を示します。

UADP ASIC 複合体

Catalyst 9500 シリーズスイッチは、2 種類の UADP ASIC で構築されています : UADP 2.0 XL と UADP 3.0 です。両方ともシステム・オン・チップ (SoC) アーキテクチャがベースになっています。両方の ASIC でそのアーキテクチャは似通っていますが、そのバージョンの違いはスイッチングキャパシティ、ポート速度、バッファリング能力、そして転送のスケーラビリティです。

UADP 2.0 XL は第 3 世代で、次世代 Catalyst の固定 or モジュラースイッチに最適化された、240G デュアルコア ASIC です。UADP 2.0 XL のアーキテクチャと機能は、全世代の UADP ASIC から大きくは変わっていません。その UADP 2.0 XL ASIC はデュアルコア アーキテクチャの 28 ナノメーター技術で構築されています。画像 11. に UADP XL ASIC のコンポーネントを示します。

UADP 2.0 XL のキーとなる能力 :

- パケット・スイッチング帯域幅 : 240G (コアあたり 120G)

- 転送パフォーマンス : 375Mpps

- スタック帯域幅 : 720G (2x360G / リング)

- FIB テーブル : 128K/64K IPv4 / IPv6 ホストルートと、64K/32K IPv4 / IPv6 最長プレフィクス該当エントリ

- 共有パケットバッファ : 32MB (コアあたり 16MB)

- 専用 NetFlow ブロック : 128K(IPv4) / 64K(IPv6) (コアあたり 64K/32K)

- TCAM ACL : 54K 全体キャパシティ

UADP 3.0 ASIC は、UADP 2.0 アーキテクチャをベースにした次世代のもので、16 ナノメーター技術により、他のすべての UADP ASICs と比べて、さらに大きなテーブルと帯域幅を提供します。画像 12. に UADP 3.0 ASIC のコンポーネントを示します。

UADP 3.0 のキーとなる能力 :

- パケット・スイッチング帯域幅 : 1600G (コアあたり 800G)

- 転送パフォーマンス : 1Bpps (コアあたり 500Mpps)

- ASIC 相互接続 : 合計 800G 帯域幅を持つ、2 つのポイント・ツー・ポイント リンク

- FIB テーブル : IPv6 の構築に最適化された、416K の 2 倍幅テーブル

- ユニファイド パケットバッファ : 両方のコアで共有の 36MB

- 専用 NetFlow ブロック : 128K(IPv4) まで、IPv6 2 倍幅共有テーブル

- TCAM ACL : 54K 全体キャパシティ

ノート : UADP 3.0 はパケット サイズ 187 バイト以上でラインレートの転送パフォーマンスを獲得しています テーブル 3. に UADP 2.0 XL と UADP 3.0 ASICs のハイレベル差分を示します

| 能力 (ASIC ごと) | Cisco Catalyst 9500

(UADP 2.0 XL) |

Cisco Catalyst 9500

ハイパフォーマンス (UADP 3.0) |

|---|---|---|

| スイッチング・転送キャパシティ | 480G / 360Mpps | 3.2Tbps / 1Bpps |

| スタック帯域幅 | 2x 360Gbps | 2x 400Gbps |

| バッファ能力 | 2x 16MB | 36MB 共有バッファ |

| スイッチ・データベース・マネージメント

(SDM) テンプレート |

固定テンプレート | 可変テンプレート |

| NetFlow 能力 | 専用 NetFlow テーブル | 共有 NetFlow テーブル |

| v4 FIB スケール | トータル 224K (*) | トータル 416K (*) |

| v4 と v6 スケール | v6 は半分 | v4 と v6 で同じスケール |

* ASIC キャパシティの最大

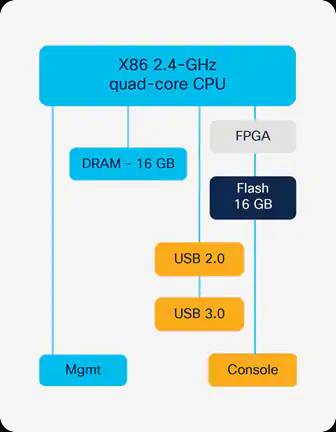

X86 CPU 複合体

Catalyst 9500 シリーズ スイッチは、同じ CPU・システムメモリー・フラッシュストレージが装備されています。画像 13 に X86 CPU 複合体の概要を示します。

- 新型 2.4Ghz x86 クアッド コア CPU (2.4Ghz 駆動 インテル Xeon-D CPU)

- シングル 16GB DDR4 2400MT/s メモリ

- ファイルシステム (前面サービス) 用外部ストレージとブルートゥースドングル用 USB タイプ A のサポート

- RJ-45 シリアルコンソールに加えて、USB mini シリアルコンソールのサポート

- 16 GB 内部エンハンスド USB (eUSB) フラッシュ

- アプリケーション ホスティングや多用途目的のストレージとして、USB 3.0 (400MB/秒 読み込み、140MB/秒 書き込み) or M.2 (300MB/秒 読み込み、290 MB/秒 書き込み) フォームファクター SSD モジュール (背面サービス)

- 手動パワーサイクルによる、スイッチのシステムリセット

ASIC 相互接続

Catalyst 9500 スイッチは、スタックポートが無い、固定型のコアと集約スイッチです。スタックポートが無いことから、ASIC 相互接続リンクは ASIC 間のコミュニケーションに使用されます。コミュニケーションは ASIC のコアもしくはコア間でローカルにスイッチングされ、ASIC 内のローカルポートに向かうパケットは ASIC 相互接続リンクを使用しません。ASIC 相互接続の目的は、複数の UADP ASICs 間のデータ移動にあります。

UADP 3.0 は 2 つの相互接続リンクを持ち、全体のパケット帯域幅は 800Gbps になります。

1 つの ASIC 相互接続は 16 SERDES (シリアライザ / デシリアライザ) の組み合わせになっており、25G NRZ フォーマットにより 400G 帯域幅で動作します。なぜならば UADP 3.0 は 2 つの ASIC 相互接続リンクを持ち、その全体帯域幅は 800Gbps であるからです。

主な UADP 3.0 ASIC 相互接続機能は以下です :

- パケットサイズ限界なし

- パケットタイプにとらわれない

- パケットデータは SERDES チャネルに散在

- ヘッダー圧縮能力

- フラグメンテーション / 順番変更 (リオーダー) なし

- ASIC 相互接続リンクでバッファリングなし

画像 14. に ASIC 相互接続のブロック ダイアグラムを示します。

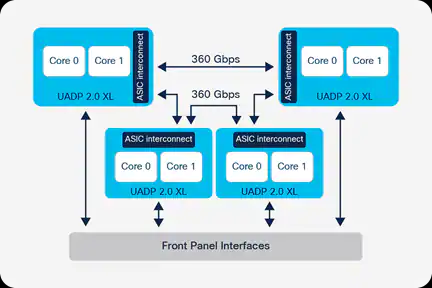

UADP 2.0 XL は実効 720G 帯域幅を持ち、それぞれの ASIC コア間は 360G です。360G は 6 つの独立 60Gbps リングからできています。(画像 15. を見てください)

フロントパネル インターフェース

イーサネット物理レイヤ (PHY) は、リンク層デバイス (多くの場合は MAC) を、トランシーバなどの物理媒体に接続します。PHY は Catalyst 9500 スイッチではイーサネットトランシーバに完全に統合されており、フロントパネルポートに挿入されたオプティクスで複数の速度 (10,25,40,100GE) をサポートするため、ASIC レーンのステアリングとマッピングをサポートします。

C9500-32C スイッチのハイライトは以下の通りです :

- 2x1 コンフィギュレーションモードに 16 列の QSFP28 ケージ

- それぞれの QSFP28 ケージは、ASIC に向かう 8 つのノースバウンド SERDES 接続を持ちます

- それぞれの SERDES は次のどちらかで動作します。40G QSFP+ オプティクスで 4x10G スピード もしくは 100G QSFP28 オプティクスで4x25G スピード

- インターフェーススピードは、挿入されたトランシーバ モジュールがベースになります

- 32 QSFP28 イーサネットポート

- QSFP+ / QSFP28 トランシーバモジュールによる 40G or 100G or CVR アダプタ + SFP による 10G/1G

- ポートマッピング

- ポート 1-8 は ASIC 0 / コア 1 , ポート 9-16 は ASIC 0 / コア 0 にマッピング

- ポート 17-24 は ASIC 1 / コア 1 , ポート 25-32 は ASIC 1 / コア 0 にマッピング

- オプティクスの電源はオンボードコントローラによって行われ、フロント パネル ケージに挿入されたモジュールで使用されます

- アドバンスド フォワーディング ASIC は、すべてのポートで 100Gbps シングル フロートラフィック処理をサポートします

画像 17. にC9500-32QC スイッチコンポーネントのハイレベル概要を提供します。

C9500-32QC スイッチのハイライトは以下の通りです :

- 2x1 コンフィギュレーションモードに 16 列の QSFP28 ケージ

- それぞれの QSFP28 ケージは、ASIC に向かう 4 つのノースバウンド SERDES 接続を持ちます

- それぞれの SERDES は次のどちらかで動作します。40G QSFP+ オプティクスで 2x20G スピード もしくは 100G QSFP28 オプティクスで4x25G スピード

- インターフェーススピードは、CLI ベース

- 32 QSFP28 イーサネットポート

- QSFP+ / QSFP28 トランシーバモジュールによる 40G or 100G or CVR アダプタ + SFP による 10G/1G

- ポートマッピング

- ポート 1-16 は ASIC 0 / コア 1 , ポート 17-32 は ASIC 0 / コア 0 にマッピング

- オプティクスの電源はオンボードコントローラによって行われ、フロント パネル ケージに挿入されたモジュールで使用されます

- デフォルトポート コンフィギュレーションは、

- ポート 1-24 は 40G インターフェースとして有効化・アクティブになります

- ポート 25-32 は 40G インターフェースですが、インアクティブです

- ポート 45-48 は 100G インターフェースとしてアクティブになります

- 100G ポートの有効化 or 無効化は、"enable / no enable" インターフェース コマンドを使用して行います

- アドバンスド フォワーディング ASIC は、100Gbps シングル フロー トラフィック処理を 100G 設定ポートでサポートし、20G シングル フロー トラフィック処理をすべての 40G ポートでサポートします

画像 18. にC9500-32QC スイッチでサポートされる、ポートコンフィギュレーションモードを示します。

画像 19. に C9500-48Y4C スイッチ コンポーネントのハイレベル概要を提供します。