「2024-08-04 Broadcom ASIC まとめ」の版間の差分

| (同じ利用者による、間の10版が非表示) | |||

| 4行目: | 4行目: | ||

* Cisco Nexus 3000 | * Cisco Nexus 3000 | ||

* Cisco NCS 5500 | * Cisco NCS 5500 , 5700 | ||

* Arista DCS | * Arista DCS | ||

* Juniper QFX5k | * Juniper QFX5k | ||

| 12行目: | 12行目: | ||

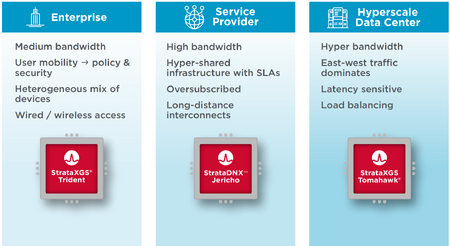

== Broadcom ASIC の適用範囲 == | == Broadcom ASIC の適用範囲 == | ||

[[ファイル:Broadcom asics.png|代替文=Broadcom asics|サムネイル|450x450ピクセル|Broadcom asics]] | [[ファイル:Broadcom asics.png|代替文=Broadcom asics|サムネイル|450x450ピクセル|Broadcom asics]]最初は Leaf の Trident , Spine の Tomahawk , ルータの Jericho と覚えとけば良いでしょう。 | ||

=== Trident === | === Trident === | ||

| 24行目: | 24行目: | ||

=== Jericho / Qumran / Ramon === | === Jericho / Qumran / Ramon === | ||

* ルータ向き | |||

* サービス プロバイダー | * サービス プロバイダー | ||

参考 URL : [https://docs.broadcom.com/doc/buyers-guide-networking-chips Networking Chips Buyer’s Guide] | 参考 URL : [https://docs.broadcom.com/doc/buyers-guide-networking-chips Networking Chips Buyer’s Guide] | ||

| 82行目: | 83行目: | ||

|拡張性向け | |拡張性向け | ||

|キャリア グレード インフラ用 | |キャリア グレード インフラ用 | ||

スケールアウト・プログラマブル・ディープバッファ | |||

|'''最適''' | |'''最適''' | ||

|'''最適''' | |'''最適''' | ||

| 96行目: | 95行目: | ||

[[ファイル:Fig2 tomahawk jericho2 dnx.webp|代替文=tomahawk vs Jericho|なし|フレーム|Tomahawk vs Jericho]] | [[ファイル:Fig2 tomahawk jericho2 dnx.webp|代替文=tomahawk vs Jericho|なし|フレーム|Tomahawk vs Jericho]] | ||

[[ファイル:Fig4 broadcom switch portfolio.webp|代替文=Broadcom ASICs Portfolio|なし|フレーム|Broadcom ASICs Portfolio]] | [[ファイル:Fig4 broadcom switch portfolio.webp|代替文=Broadcom ASICs Portfolio|なし|フレーム|Broadcom ASICs Portfolio]] | ||

== スイッチング ASIC vs プログラマブル ASIC == | |||

=== スイッチング ASIC === | |||

以前主流だった形式です。イーサネット ヘッダーや IP ヘッダに対して高速に処理できる反面、フレーム・パケット処理がハードコード (=ハードウェアで決められている) されているため機能追加はできません。 | |||

柔軟性にかける + ASIC 開発のコストを捻出するため、複数世代にわたって使えるように、マーケティングや初期の設計が重要となります。 | |||

ハードウェアにエラーや想定漏れがあると長期間修正できないため、ハードウェアの開発コストが高いです。 | |||

2003 年にリリースされて現在でも使われている、Cisco Catalyst 3750 -> 2960 -> 1000 世代の Sasquatch / Strider 系が代表的です。 | |||

=== プログラマブル ASIC === | |||

新しいヘッダであってもプログラム次第で処理が可能となる ASIC です。 | |||

自由度が高い反面、パケット処理のパイプラインを書かないといけないため、以前よりもソフトウェア開発の費用が高コストになってきているといえます。 | |||

* 5nm 世代の ASIC は、開発コストが $542.2M (=146 円換算で 791 億円) とのこと。 <ref>[https://www.janog.gr.jp/meeting/janog51/wp-content/uploads/2022/12/janog51-moore-tsuchiya.pdf ムーアの法則による高速インターフェース展開予測2025/2026] | |||

P.13 CPUチップの設計コストが高騰中</ref> | |||

例としては Cisco Catalyst 3850 に搭載の UADP ASIC が挙げられます。当初はスタンダードな機能を持つ ASIC でしたが、現在は MPLS ヘッダや VXLAN ヘッダを処理できるようになっています。 | |||

最新の Cisco Silicon One では小規模な変更でバリエーション モデルを作ることで、ルータ・スイッチに両対応してきています。 | |||

{| class="wikitable" | |||

|+プログラマブル ASIC | |||

!ASIC | |||

!P4 | |||

!NPL | |||

!備考 | |||

|- | |||

|Broadcom Trident4 | |||

| | |||

|対応 | |||

| | |||

|- | |||

|Cavium XP80 | |||

| | |||

| | |||

|ディスコン | |||

|- | |||

|Barefoot Tofino | |||

|対応 | |||

| | |||

|ディスコン | |||

顧客・アリスタでプロファイルを EOS / RPM で追加可能 | |||

Intel が開発をやめたため、今後の展開は望めない | |||

|- | |||

|Mellanox Spectrum-2 | |||

|対応 | |||

| | |||

| | |||

|- | |||

|Broadcom Jericho2 | |||

| | |||

|対応 | |||

| | |||

|- | |||

|Cisco UADP ASIC | |||

| | |||

| | |||

| | |||

|- | |||

|Cisco Silicon One | |||

|対応 | |||

| | |||

|ルータ・スイッチ用 | |||

|- | |||

|Juniper Trio | |||

| | |||

| | |||

|ルータ用 | |||

|} | |||

| 101行目: | 173行目: | ||

{| class="wikitable" | {| class="wikitable" | ||

|+スイッチ系 | |+スイッチ系 | ||

! | !シリーズ名・ | ||

コードネーム | |||

!Ver | !Ver | ||

!型式 | !型式 | ||

| 110行目: | 183行目: | ||

!Juniper | !Juniper | ||

!Extreme | !Extreme | ||

!備考 | |||

|- | |- | ||

| rowspan="6" |StrataXGS Trident | | rowspan="6" |StrataXGS | ||

Trident | |||

|[https://www.broadcom.com/products/ethernet-connectivity/switching/strataxgs/bcm56850-series 2] | |[https://www.broadcom.com/products/ethernet-connectivity/switching/strataxgs/bcm56850-series 2] | ||

|BCM56850 | |BCM56850 | ||

| 120行目: | 195行目: | ||

|QFX5100-48S | |QFX5100-48S | ||

EX4600-40F | EX4600-40F | ||

| | |||

| | | | ||

|- | |- | ||

| 130行目: | 206行目: | ||

|QFX5110-48S | |QFX5110-48S | ||

QFX5110-32Q | QFX5110-32Q | ||

| | |||

| | | | ||

|- | |- | ||

| 144行目: | 221行目: | ||

|SLX 9150 | |SLX 9150 | ||

VSP7400-48Y-8C | VSP7400-48Y-8C | ||

| | |||

|- | |- | ||

|[https://www.broadcom.com/products/ethernet-connectivity/switching/strataxgs/bcm56870-series 3-X7] | |[https://www.broadcom.com/products/ethernet-connectivity/switching/strataxgs/bcm56870-series 3-X7] | ||

| 155行目: | 233行目: | ||

|SLX 9250 | |SLX 9250 | ||

VSP7400-32C | VSP7400-32C | ||

| | |||

|- | |- | ||

|[https://www.broadcom.com/products/ethernet-connectivity/switching/strataxgs/bcm56690 4-X7] | |[https://www.broadcom.com/products/ethernet-connectivity/switching/strataxgs/bcm56690 4-X7] | ||

| 161行目: | 240行目: | ||

| | | | ||

| | | | ||

| | | | ||

| | |||

| | | | ||

| | | | ||

| 170行目: | 250行目: | ||

|132 MB | |132 MB | ||

| | | | ||

|DCS- | |DCS-7050X4 | ||

DCS-7368X4 | |||

|QFX5130-32CD | |QFX5130-32CD | ||

| | |||

| | | | ||

|- | |- | ||

| | |||

| | | | ||

| | | | ||

| 184行目: | 267行目: | ||

| | | | ||

|- | |- | ||

| rowspan=" | | rowspan="7" |StrataXGS | ||

Tomahawk | |||

|[https://www.broadcom.com/products/ethernet-connectivity/switching/strataxgs/bcm56960-series 1] | |[https://www.broadcom.com/products/ethernet-connectivity/switching/strataxgs/bcm56960-series 1] | ||

|BCM56960 | |BCM56960 | ||

| 192行目: | 276行目: | ||

|DCS-7060X | |DCS-7060X | ||

|QFX5200-32C | |QFX5200-32C | ||

| | |||

| | | | ||

|- | |- | ||

| 201行目: | 286行目: | ||

| | | | ||

|QFX5200-48Y | |QFX5200-48Y | ||

| | |||

| | | | ||

|- | |- | ||

| 206行目: | 292行目: | ||

|BCM56970 | |BCM56970 | ||

|6.4 Tbps | |6.4 Tbps | ||

| | |統合スマート | ||

バッファ 42MB<ref>https://www.arista.com/assets/data/pdf/Datasheets/7260X3_Datasheet.pdf</ref> | |||

|Nexus 3200-E | |Nexus 3200-E | ||

(N3K-C3264C-E) | (N3K-C3264C-E) | ||

|DCS-7260X3 | |DCS-7260X3 | ||

|QFX5210-64C | |QFX5210-64C | ||

| | |||

| | | | ||

|- | |- | ||

| 218行目: | 306行目: | ||

|共有 64MB <ref>https://www.arista.com/assets/data/pdf/Datasheets/7368X4-Datasheet.pdf</ref> | |共有 64MB <ref>https://www.arista.com/assets/data/pdf/Datasheets/7368X4-Datasheet.pdf</ref> | ||

| | | | ||

|DCS-7360X4 | |DCS-7060X4 | ||

DCS-7260X4 | |||

DCS-7360X4 | |||

|QFX5220-32CD | |QFX5220-32CD | ||

(128 MB <ref>[https://isp-tech.ru/data/juniper/juniper-QFX5220-datasheet.pdf QFX5220 SWITCH Data Sheet] | (128 MB <ref>[https://isp-tech.ru/data/juniper/juniper-QFX5220-datasheet.pdf QFX5220 SWITCH Data Sheet] | ||

| 227行目: | 317行目: | ||

'''128 MB'''</ref>) | '''128 MB'''</ref>) | ||

| | |||

| | | | ||

|- | |- | ||

| 237行目: | 328行目: | ||

| | | | ||

|DCS-7060X5 | |DCS-7060X5 | ||

DCS-7060DX5-64S | |||

DCS-7388X5 | |||

| | |||

| | | | ||

| | | | ||

| 244行目: | 338行目: | ||

|51.2 Tbps | |51.2 Tbps | ||

|? | |? | ||

| | |||

|DCS-7060X6 | |||

| | | | ||

| | | | ||

|[https://www.janog.gr.jp/meeting/janog53.5/doc/janog53.5_lt1.pdf LPO 対応] | |||

|- | |||

|[https://jp.broadcom.com/products/ethernet-connectivity/switching/strataxgs/bcm78910-series 6] | |||

|BCM78910 | |||

|102.4 Tbps | |||

| | |||

| | |||

| | |||

|QFX5250-64OE | |||

| | | | ||

| | | | ||

| 256行目: | 361行目: | ||

!型式 | !型式 | ||

!帯域幅 (半二重) | !帯域幅 (半二重) | ||

! | !パケット | ||

バッファ | |||

!Cisco | !Cisco | ||

!Arista | !Arista | ||

| 294行目: | 400行目: | ||

|BCM88280 | |BCM88280 | ||

|360 Gbps | |360 Gbps | ||

|GDDR6 Deep packet buffering | |||

| | | | ||

| | | | ||

| | |[https://community.juniper.net/blogs/pankaj-kumar/2022/09/13/acx7024-deepdive ACX7024] | ||

| | | | ||

|- | |- | ||

| 303行目: | 409行目: | ||

|BCM88480 | |BCM88480 | ||

|800 Gbps | |800 Gbps | ||

|Deep buffering | |Deep | ||

buffering | |||

|NCS 540 ラージ | |NCS 540 ラージ | ||

| | | | ||

| 337行目: | 444行目: | ||

| | | | ||

|- | |- | ||

| rowspan=" | | rowspan="8" |StrataDNX | ||

Jericho | Jericho | ||

|[https://www.broadcom.com/products/ethernet-connectivity/switching/stratadnx/bcm88670 1] | |[https://www.broadcom.com/products/ethernet-connectivity/switching/stratadnx/bcm88670 1] | ||

|BCM88670 | |BCM88670 | ||

|720 Gbps | |720 Gbps | ||

|VoQ Deep buffering | |VoQ Deep | ||

buffering | |||

| | | | ||

|DCS-7280R | |DCS-7280R | ||

| 362行目: | 470行目: | ||

|BCM88690 | |BCM88690 | ||

|4.8 Tbps | |4.8 Tbps | ||

|VoQ HBM Deep Buffer 2 - 16 GB <ref>https://www.arista.com/assets/data/pdf/Whitepapers/7280R3-Platform-Architecture-WP.pdf</ref> | |VoQ HBM | ||

Deep Buffer | |||

2 - 16 GB <ref>https://www.arista.com/assets/data/pdf/Whitepapers/7280R3-Platform-Architecture-WP.pdf</ref> | |||

|NCS-57B1-5DSE | |NCS-57B1-5DSE | ||

NCS-57B1-6D24H | NCS-57B1-6D24H | ||

|DCS-7280R3 | |DCS-7280R3 | ||

DCS-7280CR3 | |||

|ACX7100-32C | |ACX7100-32C | ||

ACX7100-48L | ACX7100-48L | ||

| 373行目: | 485行目: | ||

|BCM88830 | |BCM88830 | ||

|3.2 Tbps | |3.2 Tbps | ||

|Deep Buffer 4GB <ref>[https://docs.broadcom.com/doc/BCM88830-Integrated-PP-TM-and-Fabric-Interface-Single-Chip-Device-DS BCM88830 Preliminary Data Sheet] | |Deep | ||

Buffer 4GB <ref>[https://docs.broadcom.com/doc/BCM88830-Integrated-PP-TM-and-Fabric-Interface-Single-Chip-Device-DS BCM88830 Preliminary Data Sheet] | |||

Deep packet buffering, in-package HBM Gen2 for a total of 4 GB.</ref> | Deep packet buffering, in-package HBM Gen2 for a total of 4 GB.</ref> | ||

| 396行目: | 509行目: | ||

|HBM | |HBM | ||

| | | | ||

|DCS-7280R3A | |||

| | |||

| | |||

|- | |||

|[https://www.broadcom.com/products/ethernet-connectivity/switching/stratadnx/bcm88860 3] | |||

|BCM88860 | |||

|28.8 Tbps | |||

|HBM | |||

| | | | ||

| | | | ||

| | | | ||

|[https://www.janog.gr.jp/meeting/janog53.5/doc/janog53.5_lt1.pdf LPO 対応] | |||

|- | |- | ||

|[https://www.broadcom.com/products/ethernet-connectivity/switching/stratadnx/bcm88890 3AI] | |[https://www.broadcom.com/products/ethernet-connectivity/switching/stratadnx/bcm88890 3AI] | ||

| 405行目: | 527行目: | ||

| | | | ||

| | | | ||

| | |7700R4 | ||

7800R4 | |||

| | | | ||

| | | | ||

| 433行目: | 556行目: | ||

|- | |- | ||

| rowspan="2" |StrataDNX | | rowspan="2" |StrataDNX | ||

Ramon | FE9600 Ramon | ||

(fabric element) | (fabric element) | ||

| 456行目: | 579行目: | ||

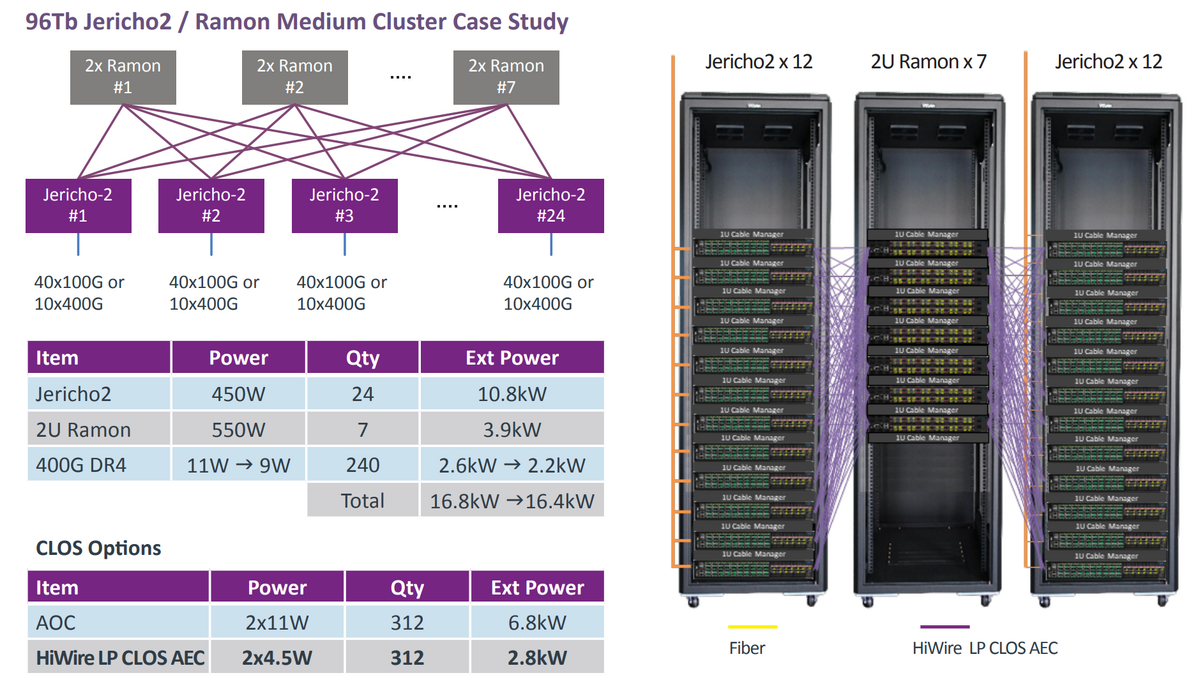

== ファブリック ASIC == | == ファブリック ASIC == | ||

ファブリック ASIC | ファブリック ASIC は Jericho 搭載シャーシ型のバックプレーンや、ホワイトボックス ルータで作る'''分散シャーシ'''の Spine で使用する。 | ||

* FE3600 | |||

* Ramon | |||

イーサネットの ECMP ベースではなく、セルベースで負荷分散を行うことで、1 つのノードであっても複数リンクを使用して負荷分散を行うことが可能。<ref>[https://www.arista.com/assets/data/pdf/Whitepapers/AI-Network-WP_jp.pdf AI ネットワーキング] | イーサネットの ECMP ベースではなく、セルベースで負荷分散を行うことで、1 つのノードであっても複数リンクを使用して負荷分散を行うことが可能。<ref>[https://www.arista.com/assets/data/pdf/Whitepapers/AI-Network-WP_jp.pdf AI ネットワーキング] | ||

| 472行目: | 598行目: | ||

* 参考 : [https://www.janog.gr.jp/meeting/janog52/wp-content/uploads/2023/08/janog52-carwg-kumaki-01.pdf キャリアバックボーンネットワークへの ホワイトボックスルータ商用化に向けた取組み] | * 参考 : [https://www.janog.gr.jp/meeting/janog52/wp-content/uploads/2023/08/janog52-carwg-kumaki-01.pdf キャリアバックボーンネットワークへの ホワイトボックスルータ商用化に向けた取組み] | ||

[[ファイル:96T J2 Ramon.png|代替文=96T J2 Ramon|なし|サムネイル|1200x1200ピクセル|96T J2 Ramon 参考 : [https://mpls.jp/2022/presentations/mpls2022-Merchant_Silicon.pdf Merchant Silicon in Carrier Networks]]] | |||

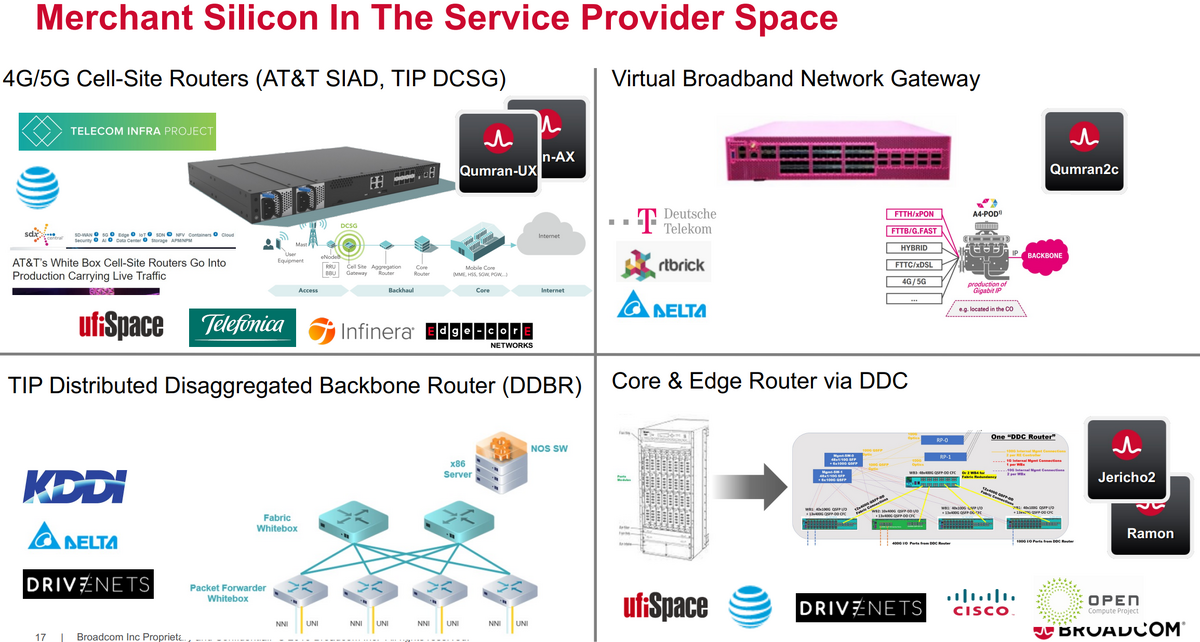

=== Cell-ste Routers , vBNG , DDC (Distributed Disaggregated Chassis) === | |||

[[ファイル:Merchant Silicon in ISP.png|代替文=Merchant_Silicon_in_ISP|なし|サムネイル|1200x1200ピクセル|Merchant_Silicon_in_ISP 参考 : [https://credosemi.com/wp-content/uploads/2021/11/Credo_HiWire_DDC_Solution_Brief_96Tb_Jericho2Ramon_062821.pdf Jericho2 & Ramon Cell Based DDC]]] | |||

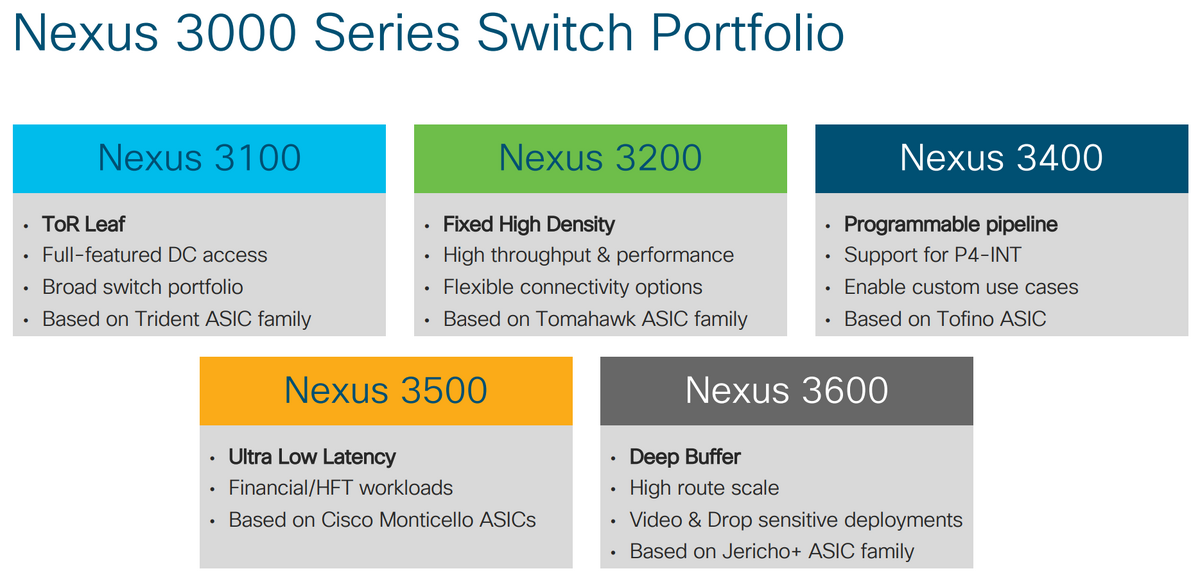

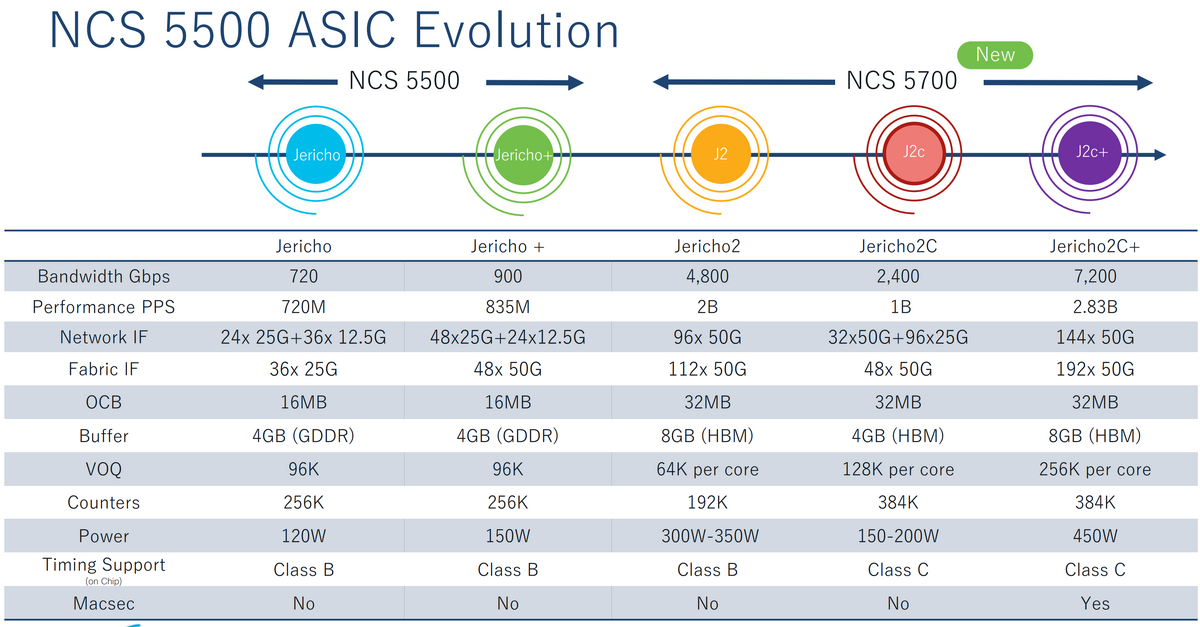

== Cisco の Broadcom ASIC 搭載製品 == | |||

== Cisco == | |||

[[ファイル:Nexus3k portfolio.png|代替文=Nexus3k portfolio|なし|サムネイル|1200x1200ピクセル|Cisco Nexus3k Portfolio]] | [[ファイル:Nexus3k portfolio.png|代替文=Nexus3k portfolio|なし|サムネイル|1200x1200ピクセル|Cisco Nexus3k Portfolio]] | ||

[[ファイル:Cisco ncs.png|代替文=Cisco ncs|なし|サムネイル|1200x1200ピクセル|Cisco NCS Portfolio]] | [[ファイル:Cisco ncs.png|代替文=Cisco ncs|なし|サムネイル|1200x1200ピクセル|Cisco NCS Portfolio]] | ||

| 492行目: | 614行目: | ||

* Cisco 7,200 vs Broadcom 14,400 | * Cisco 7,200 vs Broadcom 14,400 | ||

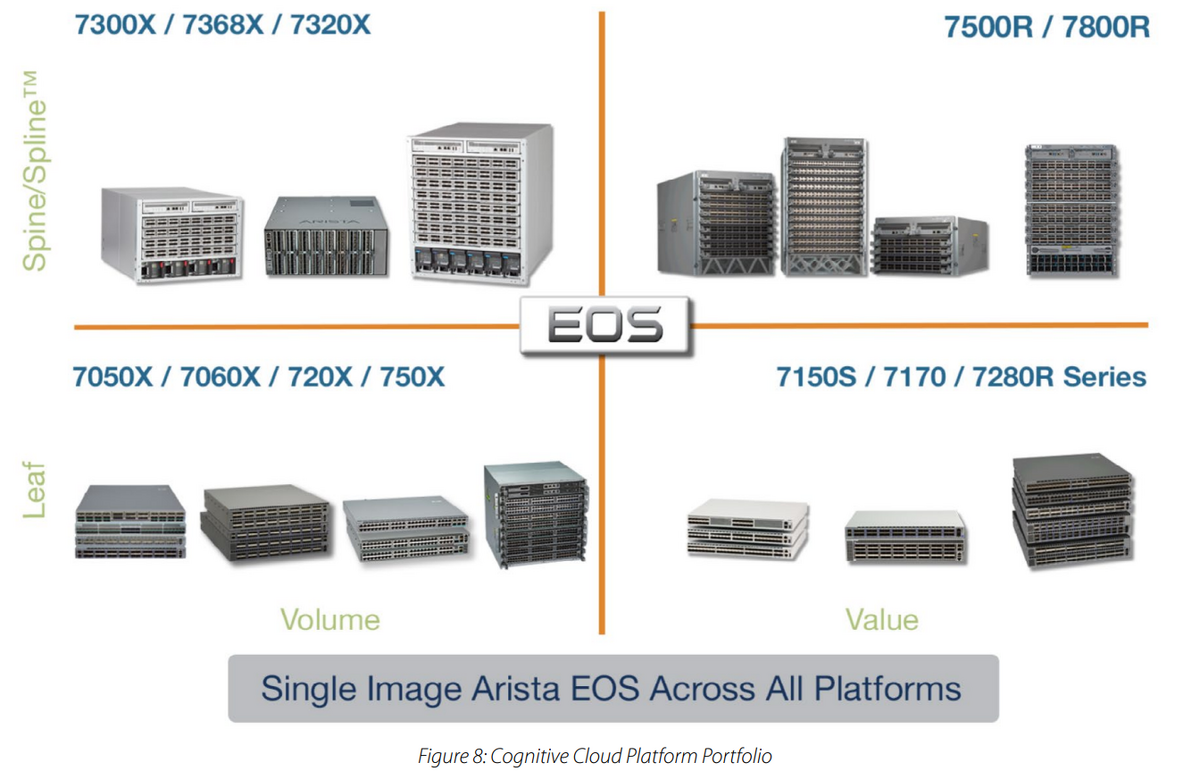

== Arista == | == Arista の Broadcom ASIC 搭載製品 == | ||

[[ファイル:Arista portfolio.png|代替文=Arista portfolio|なし|サムネイル|1200x1200ピクセル|Arista DCS Portfolio]] | [[ファイル:Arista portfolio.png|代替文=Arista portfolio|なし|サムネイル|1200x1200ピクセル|Arista DCS Portfolio]] | ||

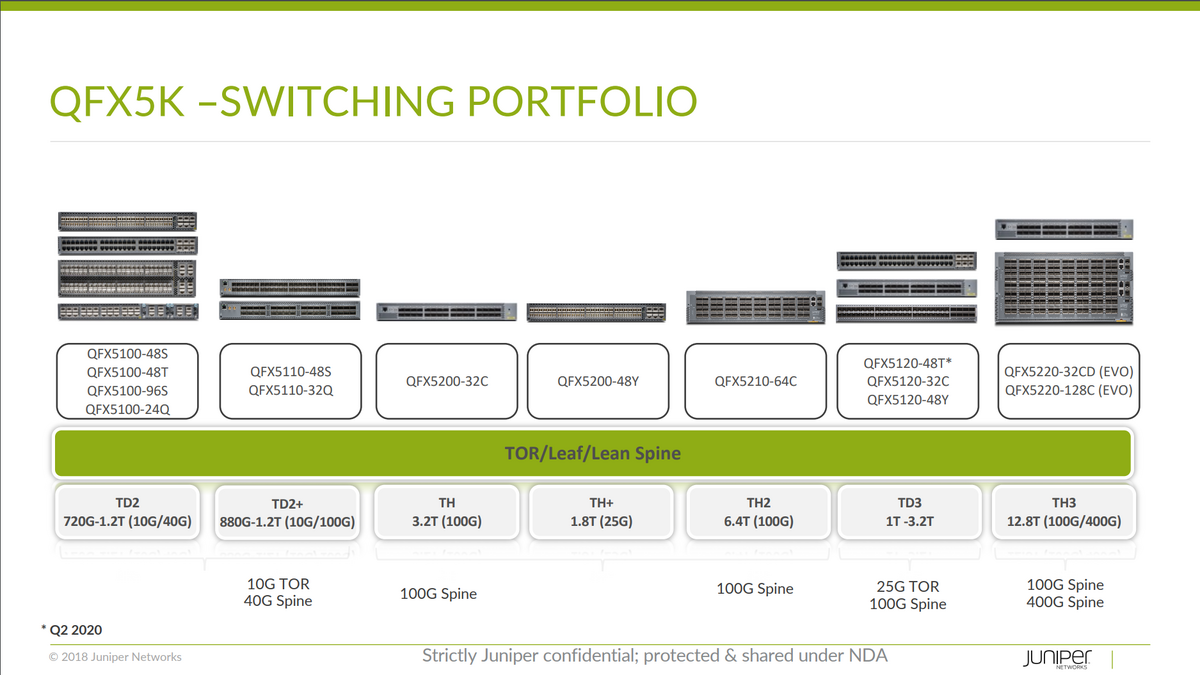

== Juniper == | == Juniper の Broadcom ASIC 搭載製品 == | ||

[[ファイル:QFX5K –SWITCHING PORTFOLIO.png|代替文=QFX5K –SWITCHING PORTFOLIO|なし|サムネイル|1200x1200ピクセル|Juniper QFX5K –SWITCHING PORTFOLIO]] | [[ファイル:QFX5K –SWITCHING PORTFOLIO.png|代替文=QFX5K –SWITCHING PORTFOLIO|なし|サムネイル|1200x1200ピクセル|[https://www.juniper.net/assets/us/en/local/pdf/nxtwork/juniper-400g-portfolio.pdf Juniper QFX5K –SWITCHING PORTFOLIO]]] | ||

== リファレンス == | == リファレンス == | ||

| 514行目: | 636行目: | ||

[https://www.juniper.net/assets/us/en/local/pdf/nxtwork/juniper-400g-portfolio.pdf JUNIPER 400G PORTFOLIO] | [https://www.juniper.net/assets/us/en/local/pdf/nxtwork/juniper-400g-portfolio.pdf JUNIPER 400G PORTFOLIO] | ||

[https://speakerdeck.com/imasaruoki/nplniyorudetapurenpuroguramingu?slide=1 NPLによるデータプレーンプログラミング] | |||

== 更新履歴 == | == 更新履歴 == | ||

| 519行目: | 643行目: | ||

2024-01-23 : ファブリック ASIC などを追記 | 2024-01-23 : ファブリック ASIC などを追記 | ||

2024-08-04 : スイッチング ASIC とプログラマブル ASIC を追記 | |||

== 引用 == | == 引用 == | ||

[[カテゴリ:その他]] | [[カテゴリ:その他]] | ||

2026年4月14日 (火) 14:51時点における最新版

Broadcom の ASIC について、情報をまとめるページです。

使われている製品として、

- Cisco Nexus 3000

- Cisco NCS 5500 , 5700

- Arista DCS

- Juniper QFX5k

- Extreme Networks VSP (旧 Avaya)

などがあります。

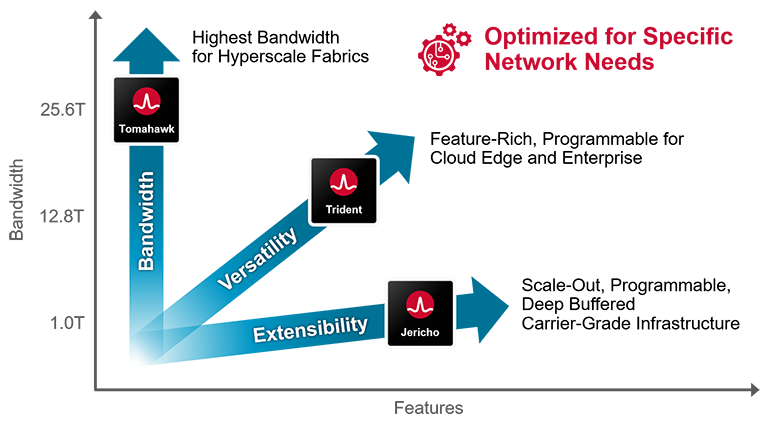

Broadcom ASIC の適用範囲

最初は Leaf の Trident , Spine の Tomahawk , ルータの Jericho と覚えとけば良いでしょう。

Trident

- エンタープライズ

Tomahawk

- ハイパースケール データセンター

Jericho / Qumran / Ramon

- ルータ向き

- サービス プロバイダー

参考 URL : Networking Chips Buyer’s Guide

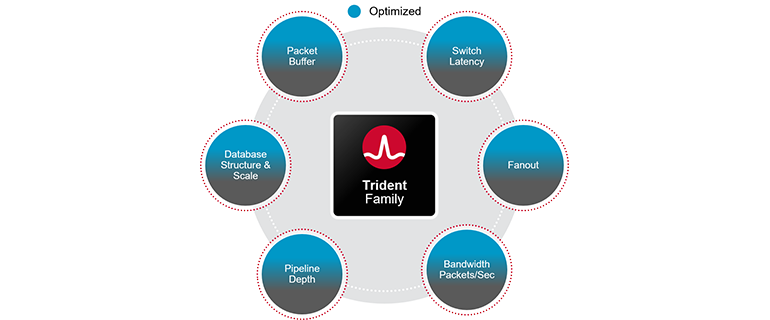

ASIC 比較表

| コードネーム | 用途 | 概要 | パケット

バッファ |

データベースの

仕組みとスケール |

パイプラインの

深さ |

テーブルの

大きさ |

スイッチの

レイテンシ |

ファン

アウト |

帯域幅

パケット/秒 |

|---|---|---|---|---|---|---|---|---|---|

| Trident | 多用途向け | クラウド エッジと

エンタープライズ用

|

普通 | 普通 | 普通 | 普通 | 普通 | 普通 | 普通 |

| Tomahawk | 高帯域幅向け | ハイパースケールの

ファブリック用

|

普通 | 普通 | 普通 | 普通 | 最適 | 最適 | 最適 |

| Jericho | 拡張性向け | キャリア グレード インフラ用

スケールアウト・プログラマブル・ディープバッファ |

最適 | 最適 | 最適 | 最適 | 普通 | 普通 | 普通 |

スイッチング ASIC vs プログラマブル ASIC

スイッチング ASIC

以前主流だった形式です。イーサネット ヘッダーや IP ヘッダに対して高速に処理できる反面、フレーム・パケット処理がハードコード (=ハードウェアで決められている) されているため機能追加はできません。

柔軟性にかける + ASIC 開発のコストを捻出するため、複数世代にわたって使えるように、マーケティングや初期の設計が重要となります。

ハードウェアにエラーや想定漏れがあると長期間修正できないため、ハードウェアの開発コストが高いです。

2003 年にリリースされて現在でも使われている、Cisco Catalyst 3750 -> 2960 -> 1000 世代の Sasquatch / Strider 系が代表的です。

プログラマブル ASIC

新しいヘッダであってもプログラム次第で処理が可能となる ASIC です。

自由度が高い反面、パケット処理のパイプラインを書かないといけないため、以前よりもソフトウェア開発の費用が高コストになってきているといえます。

- 5nm 世代の ASIC は、開発コストが $542.2M (=146 円換算で 791 億円) とのこと。 [1]

例としては Cisco Catalyst 3850 に搭載の UADP ASIC が挙げられます。当初はスタンダードな機能を持つ ASIC でしたが、現在は MPLS ヘッダや VXLAN ヘッダを処理できるようになっています。

最新の Cisco Silicon One では小規模な変更でバリエーション モデルを作ることで、ルータ・スイッチに両対応してきています。

| ASIC | P4 | NPL | 備考 |

|---|---|---|---|

| Broadcom Trident4 | 対応 | ||

| Cavium XP80 | ディスコン | ||

| Barefoot Tofino | 対応 | ディスコン

顧客・アリスタでプロファイルを EOS / RPM で追加可能 Intel が開発をやめたため、今後の展開は望めない | |

| Mellanox Spectrum-2 | 対応 | ||

| Broadcom Jericho2 | 対応 | ||

| Cisco UADP ASIC | |||

| Cisco Silicon One | 対応 | ルータ・スイッチ用 | |

| Juniper Trio | ルータ用 |

ASIC 一覧表

| シリーズ名・

コードネーム |

Ver | 型式 | 帯域幅 (半二重) | パケットバッファ | Cisco | Arista | Juniper | Extreme | 備考 |

|---|---|---|---|---|---|---|---|---|---|

| StrataXGS

Trident |

2 | BCM56850 | 1.28 Tbps | 12 MB | Nexus 3100 | DCS-7050SX-64 | QFX5100-48S

EX4600-40F |

||

| 2+ | BCM56860 | 1.28 Tbps | 16 MB | Nexus 3100-V | DCS-7050QX2-32S | QFX5110-48S

QFX5110-32Q |

|||

| 3-X5 | BCM56770 | 2.0 Tbps | 共有 32 MB [2] | DCS-7050X3-48Y8C | QFX5120-48Y

EX4650-48Y |

SLX 9150

VSP7400-48Y-8C |

|||

| 3-X7 | BCM56870 | 3.2 Tbps | 共有 32 MB [3] | Nexus 3100-Z

(N3K-C3132C-Z) |

DCS-7050X3-32C | QFX5120-32C | SLX 9250

VSP7400-32C |

||

| 4-X7 | BCM56690 | 4.0 Tbps | |||||||

| 4-X11C | BCM56890 | 12.8 Tbps | 132 MB | DCS-7050X4

DCS-7368X4 |

QFX5130-32CD | ||||

| StrataXGS

Tomahawk |

1 | BCM56960 | 3.2 Tbps | 24MB [4] | Nexus 3200 | DCS-7060X | QFX5200-32C | ||

| 1+ | 22 MB | QFX5200-48Y | |||||||

| 2 | BCM56970 | 6.4 Tbps | 統合スマート

バッファ 42MB[5] |

Nexus 3200-E

(N3K-C3264C-E) |

DCS-7260X3 | QFX5210-64C | |||

| 3 | BCM56980 | 12.8 Tbps | 共有 64MB [6] | DCS-7060X4

DCS-7260X4 DCS-7360X4 |

QFX5220-32CD

(128 MB [7]) |

||||

| 4 | BCM56990 | 25.6 Tbps | 114MB [8] | DCS-7060X5

DCS-7060DX5-64S DCS-7388X5 |

|||||

| 5 | BCM78900 | 51.2 Tbps | ? | DCS-7060X6 | LPO 対応 | ||||

| 6 | BCM78910 | 102.4 Tbps | QFX5250-64OE |

| シリーズ名・

コードネーム |

Ver | 型式 | 帯域幅 (半二重) | パケット

バッファ |

Cisco | Arista | Juniper | 備考 |

|---|---|---|---|---|---|---|---|---|

| StrataDNX

Qumran |

UX | BCM88270 | 120 Gbs | NCS 540 スモール | ||||

| MX | BCM88370 | 800 Gbps | ACX5448, ACX5448-D, and ACX5548-M | |||||

| AX | BCM88470 | 300Gbps | ||||||

| 2u | BCM88280 | 360 Gbps | GDDR6 Deep packet buffering | ACX7024 | ||||

| 2a | BCM88480 | 800 Gbps | Deep

buffering |

NCS 540 ラージ | ||||

| 2c | BCM88820 | 2.4 Tbps | HBM | |||||

| 3D | BCM88870 | 25.6 Tbps | HBM | |||||

| StrataDNX

Jericho |

1 | BCM88670 | 720 Gbps | VoQ Deep

buffering |

DCS-7280R | |||

| 1+ | BCM88680 | 900 Gbps | Nexus 3600

(N3K-C3636C-R) |

DCS-7280R2 | ||||

| 2 | BCM88690 | 4.8 Tbps | VoQ HBM

Deep Buffer 2 - 16 GB [9] |

NCS-57B1-5DSE

NCS-57B1-6D24H |

DCS-7280R3

DCS-7280CR3 |

ACX7100-32C

ACX7100-48L |

||

| 2x | BCM88830 | 3.2 Tbps | Deep

Buffer 4GB [10] |

|||||

| 2c | BCM88800 | 4.8 Tbps | NCS-57C3-MOD-SE

NCS-57C3-MOD |

ACX7509 | ||||

| 2c+ | BCM88850 | 14.4 Tbps | HBM | DCS-7280R3A | ||||

| 3 | BCM88860 | 28.8 Tbps | HBM | LPO 対応 | ||||

| 3AI | BCM88890 | 28.8 Tbps | 7700R4

7800R4 |

|||||

| StrataDNX

FE3600 (fabric element) |

BCM88770 | 3.6 Tbps | Jericho1 用ファブリック | |||||

| StrataDNX

FE9600 Ramon (fabric element) |

Ramon | BCM88790 | 9.6 Tbps | Jericho2 , 2+ と組み合わせる [11] | ||||

| 3 | BCM88920 | 51.2 Tbps | Jericho3 と組み合わせる [11] |

ファブリック ASIC

ファブリック ASIC は Jericho 搭載シャーシ型のバックプレーンや、ホワイトボックス ルータで作る分散シャーシの Spine で使用する。

- FE3600

- Ramon

イーサネットの ECMP ベースではなく、セルベースで負荷分散を行うことで、1 つのノードであっても複数リンクを使用して負荷分散を行うことが可能。[12]

- ECMP ベース : MAC / IP などをパラメータとして負荷分散

- セルベース : パケットをセルに再構成し、パラメータに依存せずに負荷分散

DDBR (Distributed Disaggregated Backbone Router)

分散シャーシは KDDI + DRIVENETS が TIP (Telecom Infra Project) で推進・商用導入 [11] された。

Feature Rich な PE よりも、バックボーンに向くとのこと。

Cell-ste Routers , vBNG , DDC (Distributed Disaggregated Chassis)

Cisco の Broadcom ASIC 搭載製品

上記 Jericho 2C と 2C+ の bandwidth Gbps は、Broadcom のページにある記載と異なります。

Broadcom の表記が全二重に見えます。

- Cisco 2,400 vs Broadcom 4,800

- Cisco 7,200 vs Broadcom 14,400

Arista の Broadcom ASIC 搭載製品

Juniper の Broadcom ASIC 搭載製品

リファレンス

Merchant Silicon in Carrier Networks

Domain-specific switch silicon in networking

Cisco SP Router Portfolio Update

Building the ACX7000 Series: the PFE

BRKDCN-3734 - Cisco Nexus 3000 Switch Architecture

The Arista Advantage Cloud Networking Trends

更新履歴

2023-10-05 : 初版作成

2024-01-23 : ファブリック ASIC などを追記

2024-08-04 : スイッチング ASIC とプログラマブル ASIC を追記

引用

- ↑ ムーアの法則による高速インターフェース展開予測2025/2026 P.13 CPUチップの設計コストが高騰中

- ↑ Trident3-X5 / BCM56770 Series 32MB of on-chip fully shared packet buffer

- ↑ https://people.ucsc.edu/~warner/Bufs/7050X3-Datasheet.pdf

- ↑ https://www.edge-core.com/temp/edm/201502edm_fileEC/A3_BROCHURE_20150206_2_view.pdf

- ↑ https://www.arista.com/assets/data/pdf/Datasheets/7260X3_Datasheet.pdf

- ↑ https://www.arista.com/assets/data/pdf/Datasheets/7368X4-Datasheet.pdf

- ↑ QFX5220 SWITCH Data Sheet QFX5220-32CD Total packet buffer 128 MB

- ↑ 400/800G Leaf and Spine solutions for hyperscale cloud and I/O intensive environments 114MB of buffers

- ↑ https://www.arista.com/assets/data/pdf/Whitepapers/7280R3-Platform-Architecture-WP.pdf

- ↑ BCM88830 Preliminary Data Sheet Deep packet buffering, in-package HBM Gen2 for a total of 4 GB.

- ↑ 11.0 11.1 11.2 DDBR HW仕様

- ↑ AI ネットワーキング セルベースのファブリック:セルベースのファブリックは、すべてのパケットを均一な大きさのセルに分割してから、すべてのファブリック・モ ジュールに均等に「スプレー(分配)」します。このスプレー動作に多くの利点があり、各転送エンジンに均等なフロー・バランスをもたらす非 常に効率的な内部スイッチング・ファブリックを実現します。セルベースのファブリックは、トラフィック・パターンに関係なく 100%効率である と考えられています。